### 特徵

統合 AVR RISC アーキテクチャ

高パフォーマンス低消費電力の RISC アーキテクチャ

12MHz で 12MIPS の処理量

SPI シリアルインターフェイス付き

アナログコンパレータ内蔵

内部クロックモードに切り替え可能

速度の目安 0~4MHz まで動作(AT90S1200-4)

0~12MHz まで動作(AT90S1200-12)

### 説明

AT90S1200 は AVR RISC アーキテクチャに基づいた低消費電力 C-MOS 8 ビットマイクロコントローラです。単一サイクルの強力な命令を実行することにより、AT90S1200 は MHz あたり 1 MIPS に及ぶ処理量を実現しており、システム設計をする上で、消費電力とプロセス速度を最適化することができます。

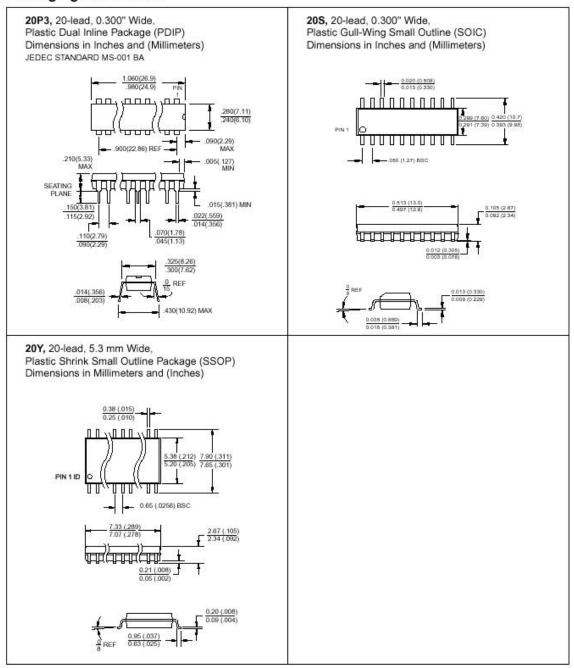

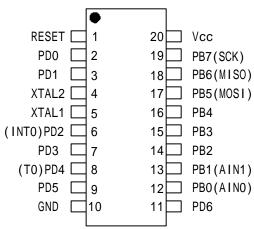

### ピン配置

### PDIP/SOIC/SSOP

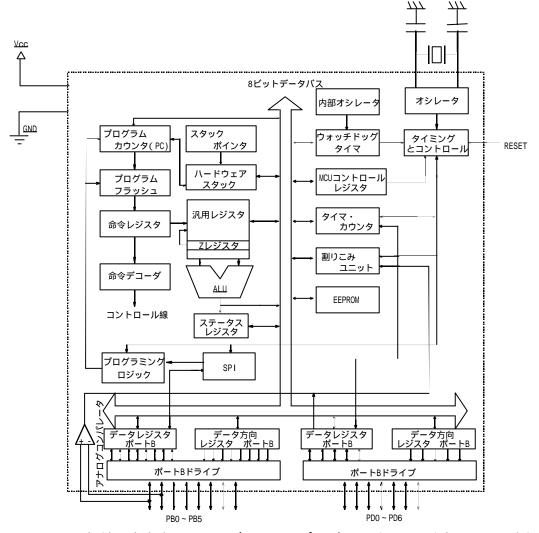

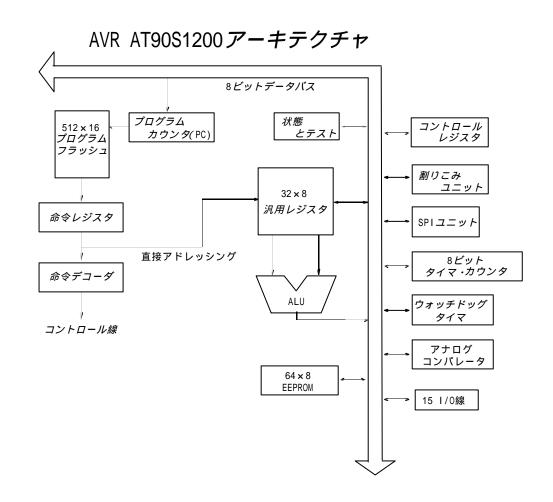

AVRの核は32の汎用レジスタを持った強力な命令と結びついています。全32レジスタは、 算術演算ユニット(ALU)に直接つながって、2つの独立なレジスタが1クロックサイク ルで実行される単一の命令でアクセスできます。結果を出すためのアーキテクチャは、従 来の CISC マイクロコントローラよりも10倍速い処理量を実現し、コード効率が良くなっています。

#### 図 1 AT90S1200 のブロックダイアグラム

アーキテクチャは極端に高密度なアセンブラコードプログラムだけでなく高レベルの言語 も効率的にサポートしています。

AT90S1200 には次のような特徴があります。1k バイトの内部プロウラミング可能なフラッシュ、64 バイトの EEPROM、15 の汎用 I/O ライン、32 個の汎用レジスタ、内部・外部割りこみ、内部クロックを使ったプログラム可能なウォッチドッグタイマ、プログラムのダウンロードのための SPI シリアルポートそして、ソフトウェアから選択可能な 2 つの省電力モードがあります。アイドルモードではレジスタ、タイマ/カウンタ、ウォッチドッグ、

割りこみシステムが機能し続けている状態で、CPU が停止しています。パワーダウンモードはレジスタの内容を保存し、次の割りこみまたはハードウェアによるリセットが行われるまで、水晶振動子を凍結、他の機能を無効にします。

デバイスは Atmel 高密度不揮発性メモリ技術を使って製造されています。内蔵フラッシュは SPI シリアルインターフェイスをとおして、または不揮発性メモリプログラマによって、プログラムメモリを内部で再プログラミングすることができます。8 ビット RISC CPU をモノリシックチップの ISP フラッシュと結びつけて、Atmel AT90S1200 は、多くの組みこんで制御する応用に対して非常に柔軟で、コスト効率のよい強力なマイクロコンとローラとなります。

AT90S1200 AVR はプログラムパッケージ・システム開発ツールをサポートしています。開発ツールはマクロアッセンブラ、プログラムデバッガ/シュミレータ、内蔵エミュレータ、評価キットを含みます。

### AT90S1200 のピンの説明

Vcc 電源供給ピン

GND グランドピン

### PORTB (PB0 ~PB2)

PORTB は8ビット双方向 I/O ポートです。ポートピンは内蔵プルアップ抵抗(それぞれのビットで ON-OFF 選択できます。)があります。PB0 と PB1 はそれぞれ、内蔵アナログコンパレータの正入力(AIN0)と負入力(AIN1)として機能します。ポート B 出力バッファは20mA までシンクでき、LED ディスプレイを直接駆動できます。PB0~PB7 のピンが入力として使われ、外部的に L レベルされている場合、プルアップ抵抗がアクティブになったときに電流源となります。ポート B ピンはリセット条件がアクティブになった時、クロックが動いていないときでもトライステートになります。

ポート B は AT90S1200 の特別機能は 30 の表にあります。

#### RESET

リセット入力。外部リセットは、たとえクロックが動いていないときでも RESET ピンに L レベルを 50ns 以上かけると起こります。短いパルスでは、リセットが生成される保証はありません。

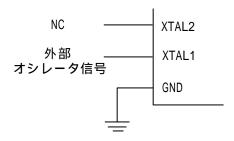

### XTAL1

振動子の反転増幅器への入力または内部クロック動作回路への入力

#### XTAL2

振動子の反転増幅器からの出力

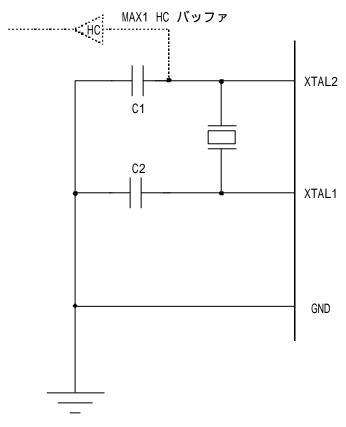

#### 水晶振動子

XTAL1 と XTAL2 は反転増幅器のそれぞれ入力と出力になっており、図 2 に示されているように内蔵オシレータのために構成されています。水晶またはセラミック共鳴子を使いま

す。外部クロックから駆動する場合は図3に示してあるように、XTAL1を駆動用に、XTAL2を接続しない状態にしておいてください。

### 図2 オシレータの接続

注意:外部デバイスのクロックとして MCU オシレータを使う場合は、図のように HC バッファを接続していなければなりません。

### 図3 外部クロック駆動のためのピン配置

### 内蔵 RC オシレータ

1MHz 固定で動く内蔵 RC オシレータは MCU のクロックソースとして選択できます。有効になった場合、AT90S1200 は外付け部品無しで動作します。 フラッシュメモリ中のコントロールビット RECN がプログラム(=0)されている場合、内蔵 RC オシレータがクロックソ

ースとして選択されます。AT90S1200 は通常このビットをプログラムしない状態(=1)で出荷しています。このビットがプログラムされている部品は、AT90S1200A で注文することができます。RCEN ビットはパラレルプログラミングのみによって変更することができます。内蔵 RC オシレータをシリアルプログラムのダウンロードに使う場合は、まず RCEN ビットをパラレルプログラミングモードでプログラムしてください。

### アーキテクチャの概要

早いアクセスをもつレジスタファイルの概念は、単一クロックサイクルのアクセス時間を持った 32\*8 ビット汎用レジスタを含んでいます。これは、1 クロックサイクルの間に 1 つの ALU (算術演算ユニット)の演算が実行されます。レジスタファイルから 2 つのオペランドが出力され、演算が実行され結果が 1 クロックサイクルで、再びたくわえられます。図 4 AT90S1200 AVR RISC アーキテクチャ

ALU レジスタ同士またはレジスタと定数での算術・論理機能をサポートしています。単一のレジスタ演算は ALU 中で実行されます。図 4 では AT90S1200 AVR RISC マイクロコン

トローラ アーキテクチャを示しています。AVR はハーバードアーキテクチャを持っており、プログラムとデータ用のメモリとバスが分かれています。プログラムは2段階のパイプラインでアクセスされます。1つの命令が実行されると、プログラムメモリから次の命令が前もって取り込まれ(フェッチされ) ます。この概念はクロックサイクル毎に実行される命令が有効になります。プログラムメモリは内部でダウンロードできるフラッシュメモリです。

比較ジャンプで呼出し命令で全 512 のアドレス空間は直接アクセスできます。全ての AVR 命令は単一の 16 ビットワードの型を持っています。プログラムメモリアドレスは 16 または 32 ビット命令を含んでいます。

割りこみまたはサブルーチン呼び出しの間、プログラムカウンタ (PC) リターンアドレス がスタックに蓄えられます。スタックは 3 段階の深さを持つハードウェアスタックで、サブルーチン呼び出しや、割りこみのために作られています。

I/O メモリ空間は、コントロールレジスタ、タイマ/カウンタ、A/D コンバータと他の I/O 機能のような CPU 周辺機能用に 64 アドレスが含まれています。AVR アーキテクチャのメモリ空間は全てリニアで規則正しいメモリマップになっています。

柔軟な割りこみモジュールは I/O 空間中でコントロールレジスタを持っており、ステータスレジスタ中に付属のグローバル割りこみ有効ビットを持っています。異なる割りこみはプログラムメモリの始めにある割りこみベクトル中にいろいろな割りこみベクトルを持っています。割りこみベクトルのアドレスが低いほど、割りこみベクトルの優先順位が高くなります。

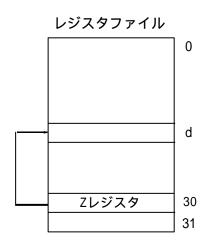

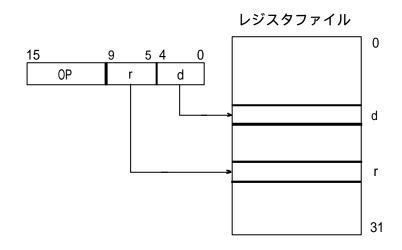

### 汎用レジスタファイル

図 5 では CPU 中の 32 汎用レジスタの構造を示しています。

図 5 AVR CPU 汎用レジスタ

汎用レジスタ

| 7           | 0 |

|-------------|---|

| R0          |   |

| R1          |   |

| R2          |   |

| R3          |   |

| • • • • • • |   |

| • • • • • • |   |

| R29         |   |

| R30(Zレジスタ)  |   |

| R31         |   |

|             |   |

命令一覧のレジスタ動作命令は全レジスタに対して直接・単サイクルアクセスを持っています。唯一の例外は、定数とレジスタ間の5つの定数算術・論理命令SBCI、SUBI、CPI、ANDI、ORI、定数データを直接ロードするLDIです。これらの命令は、後半R16~R31のレジスタファイルに適用されます。汎用のSBC,SUB,CP,AND,ORと他の2レジスタ間ま

たは 1 レジスタ上のの演算は全レジスタファイルに対して適用されます。 レジスタ 30 はレジスタファイルの間接アドレスポインタとして働いています。

### ALU 算術論理ユニット

高能力の AVR ALU は全 32 汎用レジスタと直接つながって動作します。1 クロックサイクル以内で、ALU はレジスタファイル中のレジスタ間で実行されます。ALU の演算は3つの主なカテゴリ算術・論理・ビット機能に分けられます。

### 内部プログラム可能なフラッシュプログラムメモリ

AT90S1200 は 1k バイトの内蔵 In-system プログラム可能フラッシュメモリをプログラム保存用に含んでいます。全命令は 16 ビットであるため、フラッシュは 512\*16 として組織されます。フラッシュメモリの耐久性は 1000 回の書きこみ読み込みサイクルまでになっています。

AT90S1200 プログラムカウンタ (PC) は 9 ビットの幅で、512 のプログラムメモリアドレスのアドレッシングを行います。フラッシュデータのダウンロードの詳細は 38 を見てください。

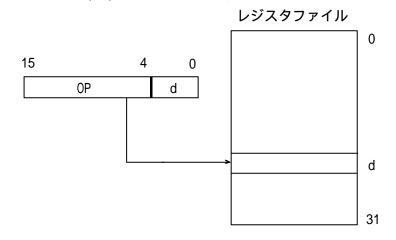

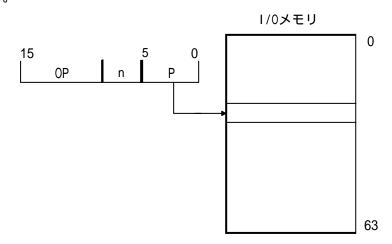

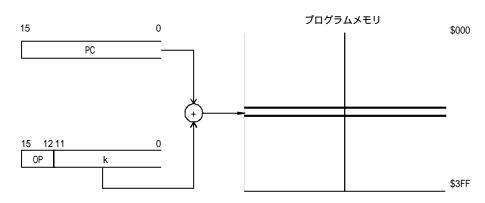

### プログラム・データアドレッシングモード

AT90S1200 AVR RISC マイクロコントローラは強力で効率の良いアドレッシングモードをサポートしています。この節では、AT90S1200d デサポートされているアドレッシングモードについて説明しています。図において、OP は命令ワードに対する動作コードのことです。単順に、すべての図がアドレッシングビットの正確な位置を示しているわけではありません。

### 直接レジスタ、単一レジスタRd

図 6 直接単一レジスタアドレッシング オペランドはレジスタ d(Rd)に含まれています。

### 間接レジスタ

アクセスされるレジスタは Z レジスタ(R30)によって指定されます。

### 直接レジスタ、2 つのレジスタ Rd と Rr

図 8 直接アドレッシング、2 つのレジスタ

オペランドはレジスタ r(Rr)と d(Rd)に含まれています。結果は d に蓄えられます。

### 直接 I/0

図 9 I/O 直接アドレッシング

オペランドは命令ワード中の 6 ビットに含まれています。n は行き先またはもとのレジスタアドレスです。

### 相対プログラムアドレッシング、RJMP とICALL

図 10 相対プログラムメモリアドレッシング

プログラムは PC+k+1 のアドレスで実行されます。相対アドレス k は- $2048 \sim 2047$  までになります。

### サブルーチンとハードウェアの割りこみスタック

AT90S1200 はサブルーチンと割りこみに対して3段階の深さをもつハードウェアスタックを使っています。ハードウェアのスタックは9ビット長あり、サブルーチンや割りこみが実行されている間プログラムカウンタの戻りアドレスを保存しています。

RCALL命令と割りこみはスタックレベル0上に push されたのスタックレベル $1\sim2$ では、さらにしたのスタックに push されます。RET と RETI 命令が実行されるとき戻ってくる PC はスタックレベル0 からフェッチされ(持ってこられ)、他のスタックレベル $1\sim2$  がスタックから 1 レベル pop されます。3 以上のサブルーチン呼びだしや、割りこみが実行されると、スタックに書きこまれている最初の値が上書きされていきます。

### EEPROM データメモリ

AT90S1200 は 64 バイトの EEPROM データメモリを持っています。単一のバイトの読み込みと書きこみができる別のデータスペースとして編成されています。EEPROM は最低100000 回の読み込みまたは書きこみの耐久性があります。EEPROM と CPU のアクセスは 25 ページに説明されており、EEPROM アドレスレジスタ、EEPROM データレジスタ、EEPROM コントロールレジスタを指定します。SPI のデータダウンロードについての詳しい説明は 45 ページを見て下さい。

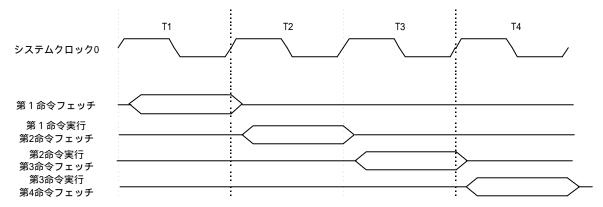

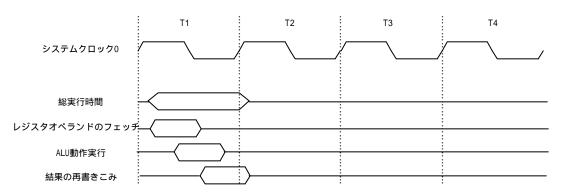

### メモリアクセス・命令実行時間

この節では、命令の実行と内部のメモリアクセスについて、一般的なアクセスの概念を説明します。

AVR CPU はシステムクロック 0 で駆動され、チップ用の外部クロックから直接生成されます。内部クロックによる分周が使われています。

図 11 はハーバードアーキテクチャと高速アクセスのレジスタファイルの概念によって可能になった並列的に命令フェッチと命令の実行をする様子をあらわしています。これが MHz あたり 1MIPS まで得ることのできる基本的なパイプラインの概念です。それに対応した時間コスト、クロック、電力単位あたりの動作結果を持ちます。

図 11 並列命令フェッチ・命令の実行

図 12 単サイクルでの ALU 動作

図 12 は、レジスタファイルの内部でのタイミングの概念を表しています。単クロックサイクルで、2 つのレジスタオペランドを使った ALU 演算が実行され、結果は行き先レジスタ へ蓄えられます。

#### I/O メモリ

AT90S1200の I/O 空間の定義は次の表に示されています。

表 1 AT90S1200 の I/O 空間

| 16進アドレス    | 名称     | 機能                   |

|------------|--------|----------------------|

| \$3F(\$5F) | SREG   | ステータスレジスタ            |

| \$3B(\$5B) | GIMASK | 一般割りこみマスクレジスタ        |

| \$39(\$59) | TIMSK  | タイマ/カウンタ割りこみマスクレジスタ  |

| \$38(\$58) | TIFR   | タイマ/カウンタ割りこみフラッグレジスタ |

| \$35(\$55) | MCUCR  | MCUコントロールレジスタ        |

| \$33(\$53) | TCCR0  | タイマ/カウンタ0コントロールレジスタ  |

| \$32(\$52) | TCNT0  | タイマ/カウンタ0 (8ビット)     |

| \$21(\$41) | WDTCR  | ウォッチドッグタイマコントロールレジスタ |

| \$1E(\$3E) | EEAR   | EEPROMアドレスレジスタ       |

| \$1D(\$3D) | EEDR   | EEPROMデータレジスタ        |

| \$1C(\$3C) | EECR   | EEPROMコントロールレジスタ     |

| \$18(\$38) | PORTB  | PORTBデータレジスタ         |

| \$17(\$37) | DDRB   | PORTBデータ方向レジスタ       |

| \$16(\$36) | PINB   | PORTB入力ピン            |

注意:予約・不使用の位置については表には示していません。

AT90S1200 の I/O と周辺は I/O 空間に置かれています。I/O は 32 の汎用レジスタと I/O 空間の間を転送する IN と OUT 命令で、アクセスします。アドレス範囲 $\$00 \sim \$1F$  内の I/O レジスタは SBI,CBI 命令を使うことにより直接ビットアクセスをすることができます。これらのレジスタにおいて、単一ビットの値は SBIS,CBIC 命令を使ってチェックすることができます。詳しくは、命令一覧の章を見てください。

これからの、デバイスとの互換性のために、予約ビットはアクセスされた場合、0 で書きこまれていなければなりません。予約 I/O メモリのアドレスには書きこまないでください。 ステータスレジスタの中には、1 を書きこんでクリアできるものもあります。CBI と SBI 命令は I/O ビットの全ビットで動作し、セットで読まれているどのフラッグに 1 を書きこみなおすことができ、これによりフラッグがクリアされます。CBI と SBI 命令は\$00 から\$1F のレジスタのみで動作します。

I/O レジスタと周辺コントロールレジスタは次の節で説明されています。

### ステータスレジスタ SREG

AVR ステータスレジスタ SREG は I/O 位置\$3F(\$5F)にあり、次のように定義されます。

ビット 7 I: グローバル割りこみ有効

グローバル割りこみビットを、割りこみを有効にさせるためには1に設定されなければな

りません。設定してはじめて、個々の割りこみ有効コントロールは、別のコントロールレジスタで実行されます。グローバル割りこみ有効レジスタが 0 にクリアされると、割りこみは個々の割りこみイネーブルの設定と無関係になり、割りこみが実行されることはありません。割りこみでハードウェアによって I ビットがクリアされたあと、RETI 命令によって設定され、後に続く割りこみが有効になります。

### ピット 6 T: ビットコピーメモリ

ビットコピー命令 BLD(Bit LoaD ロード)と BST(Bit STore 保存)により、(レジスタ中の) ビットは T ビットがソースとして、T ビットへの保存先として演算されます。レジスタファイル中のビットは BST 命令によって T ヘコピーされ、T 中のビットは BLD 命令によりレジスタファイル中の(指定した)1 ビットへコピーされます。

### ピット 5 H: ハーフキャリーフラッグ

ハーフキャリーフラッグ H は、ある算術演算のハーフキャリーフラッグを示しています。 詳細については、命令一覧を参照してください。

### ビット4 S: サインビット

S ビットは負フラッグと 2 の補数オーバーフローフラッグの排他的 OR をとっています。詳しい情報については命令一覧を参照してください。

### ビット3 V:2 の補数オーパーフローフラッグ

2 の補数オーバーフローフラッグ V は、2 の補数算術演算ができます。詳細は命令一覧を見てください。

### ビット2 N:負フラッグ

負フラッグ N 算術・論理演算で負の結果が出たことを示します。詳しい情報については、 命令一覧の説明を見てください。

### ピット1 Z:ゼロフラッグ

ゼロフラッグ Z は算術・論理演算でゼロの結果が出たことを示しています。詳しい情報については、命令一覧の説明を見てください。

#### ビット 0 C:キャリーフラッグ

キャリーフラッグは算術・論理演算でキャリー(桁上げ・桁下げ 訳者注)の結果が出たことを示しています。詳しい情報については、命令一覧の説明を見てください。

注意 ステータスレジスタは、割りこみルーチンに入ったときに自動的に蓄えられたり、返ってきたときに自動的に戻されることはありません。この処理は、ソフト上で行ってください。

### リセットと割りこみの扱い

AT90S1200 は3つの割りこみソースがあります。これらの割りこみとリセットベクトルは、 プログラムメモリ空間中に別のプログラムベクトルを持っています。 どの割りこみも個々 にイネーブルビットを持っており、割りこみを有効にするためにステータスレジスタ中の I

ビットと一緒に設定します。

プログラムメモリ空間の最低アドレスは、リセットと割りこみベクトルとして自動的に定義されます。ベクトルの完全な表は、表 2 に示してあります。リストでは割りこみの優先レベルが決まっています。低いアドレスほど優先順位が高くなります。RESET は最も優先順位が高く、次に外部割りこみ要求 0: INTO などと続きます。

表 3 リセット・割りこみベクトル

| ベクトル<br>番号 | プログラム<br>アドレス | ソース        | 割りこみの定義                         |

|------------|---------------|------------|---------------------------------|

| 1          | \$000         | RESET      | ハードウェアのピン、パワーオンリセット、ウォッチドッグリセット |

| 2          | \$001         | INT0       | 外部割りこみ要求0                       |

| 4          | \$002         | TIMER0,OVF | タイマ/カウンタ0オーバーフロー                |

| 5          | \$003         | ANA_COMP   | アナログコンパレータ                      |

### 最も典型的なリセットと割りこみのアドレスは

アドレス ラベル コード コメント

\$000 rjmp reset ;リセットのハンドラ

\$001

rjmp EXT\_INT0

;外部割りこみ要求 0のハンドラ

\$002

rjmp TIM0\_OVF0

;タイマ 0 オーバーフローのハンドラ

\$003

rjmp ANA\_COMP

;アナログコンパレータのハンドラ

\$004

MAIN:

<命令> ~

;メインプログラムの始まり

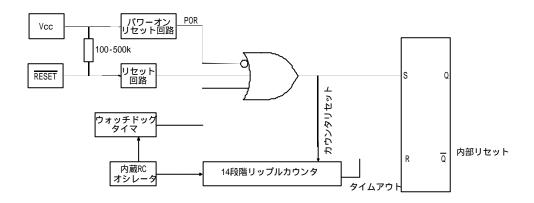

#### リセットソース

AT90S1200 は3 つのリセット源を持ちます。

- ・パワーON リセット MCU は供給電源がパワーオンリセットスレッシュホールド Vpot を下回るときに、リセットされます。

- ・外部リセット RESET ピンに 50ns 以上 L レベルがあると MCU がリセットされます。

- ・ウォッチドッグリセット ウォッチドッグリセット期間が終了し、ウォッチドッグが有効になったときに MCU がリセットされます。

リセット期間中、すべての I/O レジスタが初期値に設定され、プログラムはアドレス\$000 から実行を開始します。アドレス\$000 に設定された命令は、扱っているルーチンをリセットするために RJMP 命令:相対ジャンプでなければなりません。プログラムが割込み源をイネーブルしない場合、割りこみベクトルは使われることはないので。そこに普通のプログラムコードを置くことができます。図 13 の回路図はリセットのロジックを表しています。表 3 でリセット回路の時間と電気的なパラメータを定義しています。パワーオンリセットのタイミングは内蔵 RC オシレータによってクロックされます。他の Vcc 電圧での RC オシレータに対する周波数特性のデータを参照してください。

### 図 13 リセットの論理

表 3 リセットの特徴 (Vcc=5.0)

| 記号                | パラメータ                             | 最小值 | 標準値 | 最大值     | 単位 |

|-------------------|-----------------------------------|-----|-----|---------|----|

| $V_{POT}$         | パワーオンリセットスレッシュホールド電圧 位ち上がり)       | 0.8 | 1.2 | 1.6     | V  |

| V POT             | パワーオンリセットスレッシュホールド電圧 位ち下がり)       | 0.2 | 0.4 | 0.6     | V  |

| $V_{RST}$         | RESETピンスレッシュホールド電圧                |     |     | 0.85Vcc | V  |

| $t_{TOUT}$        | パワーオンリセット周期                       | 2   | 3   | 4       | ms |

| t <sub>TOUT</sub> | リセット遅延タイムアウト周期 (タイムアウト周期はWDTの16k倍 | 11  | 16  | 21      | ms |

|                   | のサイクルと等しくなります。いろいろな電圧でのWDTの標準周    |     |     |         |    |

|                   | 波数については2-50ページの 標準特性」を参照して下さい。)   |     |     |         |    |

注 1:パワーオンリセットは供給電圧が Vpot (立ち下がり)以下にならないばあい起こりません。

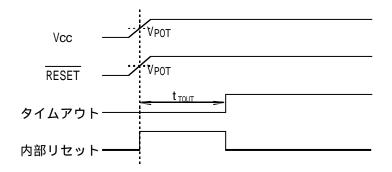

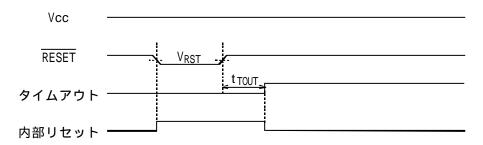

### パワーオンリセット

パワーオンリセット(POR)回路によりデバイスはパワーオンからリセットされます。図 13 に示されているように、ウォッチドッグタイマオシレータからクロックされる内部タイマ により、MCU が動き始めないようにしてあり、Vcc の立ち上がり時間にかかわらず、Vcc がパワーオンリセットスレッシュホールド電圧  $V_{POT}$  に達してからしばらく動きません。(図 14 参照)

図 14 MCU スタートアップ、Vcc に結びついた RESET

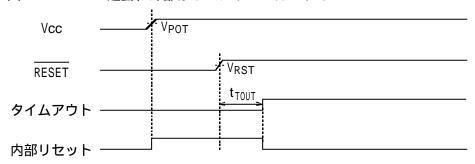

内蔵起動の遅延回路が有効である場合は、RESET は直接 Vcc につながっており、外部プルアップ抵抗をとおして直接つなぐことができます。RESET ピンを Vcc が加えられてからしばらくの間 L レベルにしておくことにより、パワーオンリセットの期間が延長されます。これについてのタイミングの例に付いては図 15 を参照してください。

図 15 MCU の起動、外部からコントロールされる RESET

### 外部リセット

外部リセットは RESET ピン上に L レベルを加えることによって生成されます。50ns より 長いリセットパルスがかかっていると、たとえクロックが動いていない場合でも、リセットが生成されます。これより短いパルスではリセットが生成される保証はありません。加えられた信号が立ち上がりでスレッシュホールド電圧 Vrst になるとき、タイムアウト時間 Ttout が終わった後、遅延タイマにより MCU が始動します。

図 16 動作中の外部リセット

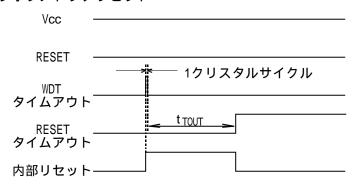

#### ウォッチドッグリセット

ウォッチドッグタイマが時間切れになると、1 XTAL のサイクルの継続時間の短いリセットパルスを生成します。このパルスの立ち下がりが起こると、遅延タイマが時間切れ時間 trourのカウントを開始します。ウォッチドッグの動作の詳細については 23 ページを参照してください。

図 17 動作中のウォッチドッグリセット

### 割りこみの扱い

AT90S1200 は 2 つの 8 ビット割りこみマスクコントロールレジスタ GIMSK (汎用割りこみマスクレジスタ: I/O アドレス\$3B) と TIMSK (タイマ/カウンタ割りこみマスクレジスタ: I/O アドレス \$39) を持っています。

割りこみが起こるとき、グローバル割り込み有効 I ビットがクリア(0)され、すべての割りこみが無効になります。ソフトウェア上でI ビットをI に設定でき、これによりネストされた割りこみが有効になります。割りこみからの帰還命令 RETI が実行されると、I ビットがI に設定されます。

対応する割りこみ有効ビットが 0 になった時に割りこみ条件が起こるとき、割りこみフラッグが設定され、割りこみが有効になるか、ソフト上でフラッグが消去されるまで記憶されます。

グローバル割りこみ有効ビットがクリアになったとき一つ以上の割りこみ状態起こっている場合、対応する割りこみフラッグが設定され、グローバル割り男込みビットが有効になった後優先順位に従って実行されるまで、記憶されています。外部レベル割り込みではフラッグを持たないことに注意してください。このため、割りこみ状態がアクティブなときだけ、記憶されています。

ステータスレジスタは、割りこみルーチンに入るときに自動的に蓄えられたり、割りこみルーチンから返ってきたときに、元に戻されることはありませんので注意してください。 これはソフト上で処理を行ってください。

### 一般割りこみマスクレジスタ GIMSK

**ビット7 Res**: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に0 として 読み込まれます。

### ビット 6 INTO:外部割りこみ要求 0 有効ビット

INTO が 1 に設定されていて、ステータスレジスタ(SREG)中の I ビットが 1 に設定されている場合、外部ピン割りこみが有効になります。MCU コントロールレジスタ MCUCR 中の割り込み感度コントロール 0 ビットは 1/0(ISC01 と ISC00)は外部割りこみが、立ち上がり、立ち下がり、L レベルでアクティブになるかどうかを定義しています。出力として INTO ピンが構成されている場合でも、ピン上にくわわる変化で割りこみが生じます。18 ページを参照してください。

**ビット 5~0 Res**: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

### タイマ/カウンタ割りこみマスクレジスタ TIMSK

| ビット _      | 7      | 6      | 5       | 4       | 3      | 2      | 1                     | 0      | _     |

|------------|--------|--------|---------|---------|--------|--------|-----------------------|--------|-------|

| \$39       | -      | -      | -       | -       | -      | -      | TOIE0                 | -      | TIMSK |

| -<br>読み込み・ | 読      | 読      | 読       | 読       | 読      | 読      | 読/書                   | 読      | =     |

| 書きこみ       | (Read) | (Read) | (R ead) | (R ead) | (Read) | (Read) | (R ead) /<br>(W rite) | (Read) |       |

| 初期值        | 0      | 0      | 0       | 0       | 0      | 0      | 0                     | 0      |       |

ビット 7~2 Res: 予約ビット

これらのビットは AT90S1200 の予約ビットで、常に0 として読み込まれます。

### ビット1 TOIEO:タイマ/カウンタオーバーフロー割りこみ有効

TOIE0 ビットが 1 に設定されていて、ステータスレジスタ中の I ビットが 1 に設定されている場合、タイマ/カウンタ 0 オーバーフロー割りこみが有効になります。タイマ 0 カウンタの中でオーバーフローが起こったとき対応する割りこみ(アドレス\$002)が実行されます。このとき、タイマ/カウンタ割りこみフラッグレジスタ TIFR 中の TOV0 ビットが 1 に設定されます。

**ビット 0 Res**: 予約ビットこのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

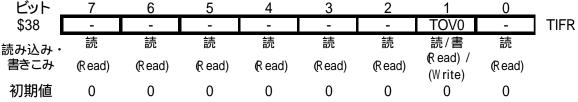

### タイマ/カウンタ割りこみフラッグレジスタ TIFR

**ビット 7~2** Res: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

### **ビット1 TOV0**:タイマ/カウンタオーバーフローフラッグ

タイマ/カウンタ0でオーバーフローフローが起こるとき、TOV0が1に設定されます。TOV0は、対応する割りこみベクトルが実行されるときに、ハードウェアによってクリアされます。代わりに、TOV0は論理1をフラッグへ書きこむことにより、クリアされます。SREG

の I ビット、TOIE(タイマ/カウンタオーバーフロー割りこみイネーブル)と TOV0 が 1 に設定されているとき、タイマ/カウンタ 0 オーバーフロー割り込みが実行されます。

**ビット 0 Res**: 予約ビットこのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

#### 外部割りこみ

割りこみ応答時間

外部割りこみは INTO ピンによってトリガされます。割りこみは立ち上がり・立ち下がり L レベルでトリガされます。これは MCU コントロールレジスタ MCUCR の仕様に示されて いるとおりに設定することができます。

外部割りこみがトリガされていて、レベルトリガになっている場合、ピンが L レベルになっている限り割り込みが依存(pending) します。(訳者注: AT90S2343 では「トリガされる」と書いてありますが、ここでの正確な意味は不明。)

割りこみは INTO ピンが出力として構成されている場合でも、割りこみはトリガされます。 これによりソフトウェアによる割りこみが可能になります。

割りこみフラッグは直接アクセスすることはできません。外部エッジでトリガされた割り 込みが依存関係にあるかもしれない場合は、次のようにしてフラッグを消すことができま す。

- 1. GIMSK 中の INTO を消去することにより外部割りこみを無効にできます。

- 2. レベルトリガ割りこみを選択してください。

- 3. 望みの割りこみエッジを選択してください。

- 4. GIMSKの INTO を設定することにより外部割りこみをもう一度有効にしてください。

有効になった AVR の割り込みに対する割りこみ実行応答時間は、最小で 4 クロックサイクルです。割りこみフラッグが設定されてから、4 クロックサイクルで、実際に動いている割りこみルーチンのプログラムベクトルのアドレスが実行されます。これらの 4 サイクルのうち、プログラムカウンタ (9 ビット) はスタックへ POP されます。ベクトルは割りこみルーチンへの相対ジャンプで、ジャンプは 2 クロックかかります。マルチサイクル命令が実行されている間に割り込みが起こった場合、この命令は割りこみが働くまでに完了します。

割りこみルーチンから返ってくる(サブルーチンの呼び出しも同様)のには 4 サイクルかかります。これらの 4 サイクルの間、プログラムカウンタ (9 ビット)が POP でスタックから戻され、SREG 中の I フラッグが設定されます。AVR が割りこみから抜け出すとき、常にメインプログラムへもどり、未実行の割りこみが実行される前に 1 つ命令を実行します。

サブルーチンと割りこみスタックが3段階のハードウェアスタックで、3以上ネストしているサブルーチンや割りこみが実行された場合は最新の3アドレスまでが保存されています。

### MCU コントロールレジスタ MCUCR

MCU コントロールレジスタは、一般の MCU 機能に対するコントロールのためのビットを含んでいます。

| ビット        | 7      | 6      | 5        | 4        | 3      | 2      | 1        | 0        | _     |

|------------|--------|--------|----------|----------|--------|--------|----------|----------|-------|

| \$35       | -      | -      | SE       | SM       | -      | -      | ISC01    | ISC00    | MCUCR |

| -<br>読み込み・ | 読      | 読      | 読/書      | 読/書      | 読      | 読      | 読/書      | 読/書      | _     |

| 書きこみ       | (Read) | (Read) | (Read) / | (Read) / | (Read) | (Read) | (Read) / | (Read) / |       |

|            | ()     | ()     | (W rite) | (W rite) | (1000) | (1000) | (W rite) | (W rite) |       |

| 初期値        | 0      | 0      | 0        | 0        | 0      | 0      | 0        | 0        |       |

**ビット 7,6 Res**: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

### ビット 5 SE: スリープ有効

スリープ命令が実行されるときに MCU をスリープモードに入らせるために、SE ビットは 1 に設定されていなければなりません。MCU が勝手に(プログラム上の意図がない限り) スリープモードに入ってしまわないようにするために、SLEEP 命令の実行する直前にスリープモードを設定することをお勧めします。

### ビット4 SM: スリープモード

このビットで 2 つのスリープモードを選択します。SM が 0 になっていると、スリープモードとしてアイドルモードが選択されます。SM が 1 に設定されると、スリープモードとしてパワーダウンモードが選択されます。詳しくは次のページの「スリープモード」を参照してください。

**ビット 3,2 Res:** 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

**ビット 1,0 ISC01,ISC00**:割りこみ感度コントロール 0 ビット 1、ビット 0 外部割りこみ 0 は、SREG の I フラッグと GIMSK 中の対応する割りこみマスクが設定されている場合、外部ピン INTO によって、アクティブになります。割りこみがアクティブになら外部 INTO ピンのレベル、エッジは次の通りです。

表 4 割りこみ 0 感度コントロール

| ISC01 | ISC00 | 説明                             |

|-------|-------|--------------------------------|

| 0     | 0     | NTO上でLレベルになると割りこみ要求が起こります。     |

| 0     | 1     | 予約                             |

| 1     | 0     | NTO上で立ち下がりエッジがあると割りこみ要求が起こります。 |

| 1     | 1     | NTO上で立ち上がりエッジがあると割りこみ要求が起こります。 |

注意: ISC01/ISC00 ビットを変えるとき、INTO は GIMSK レジスタ中の割りこみイネーブルビットをクリアすることにより無効にしておかなければなりません。そうしないと、ビットを変えた時に割りこみが起こることがあります。

INT01 ピンの値がエッジを検知する前にサンプリングされます。エッジまたはトグル割り込みが選択されていると、1 クロック周期より長いパルスにより割りこみが生成されます。

L レベル割りこみが選択されている場合、割りこみを生成するために今実行している命令が 完結するまで L レベルが保たれていなければなりません。レベルトリガ割りこみが有効に なっている場合は、ピンが L レベルに保てれている限り割りこみ要求が生成されます。

### スリープモード

スリープモードに入るためには、MCUCR 中の SE ビットを 1 に設定し、SLEEP 命令が実行されなければなりません。スリープモードに MCU が入っている間に、有効になった割りこみが起こった場合、MCU が目を覚まし、割りこみルーチンを実行し、SLEEP に続く命令から実行を再開します。レジスタファイル、SRAM、I/O メモリの内容が変わることはありません。スリープモード時にリセットが起こった場合は、MCU は目覚めて、リセットベクトルから実行していきます。

#### アイドルモード

SM ビットが 0 にクリアされると、SLEEP 命令で MCU は強制的にアイドリングモードに入って、CPU は止まりますが、タイマ/カウンタ、ウォッチドッグタイマ、割りこみシステムが動きつづけています。これにより、MCU は、タイマオーバーフローやウォッチドッグリセットなどのような内部割込みだけではなく、外部トリガによる割りこみで目覚めます。アナログコンパレータ割りこみからの起動が必要でない場合は、アナログコンパレータコントロール・ステータスレジスタ ACSR 中の ACD ビットを設定することにより、アナログコンパレータはパワーダウンされます。これにより、アイドルモードでの消費電力を減らすことができます。MCU がアイドルモードから起動すると、CPU は直ちにプログラムの実行を開始します。

### パワーダウンモード

SM ビットが 1 に設定されていると、SLEEP 命令で MCU が強制的にパワーダウンモードに入ります。このモードでは、外部割りこみや(有効になっている場合)ウォッチドッグが動作しつづけている一方で、外部オシレータは停止します。外部リセット、ウォッチドッグリセット、INTO ピン上の外部レベル割りこみだけが、MCU を目覚めさせることができます。

レベルトリガ割りこみがパワーダウンモードからの起動に使われている場合、変化したレベルは MCU を起動するのに、リセット遅延タイムアウト周期 trout より長く保たれていなければなりません。送でない場合は、デバイスが起動することはありません。

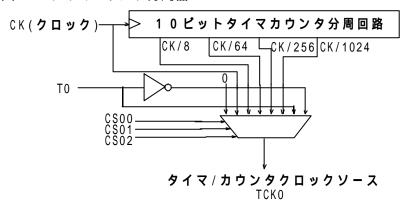

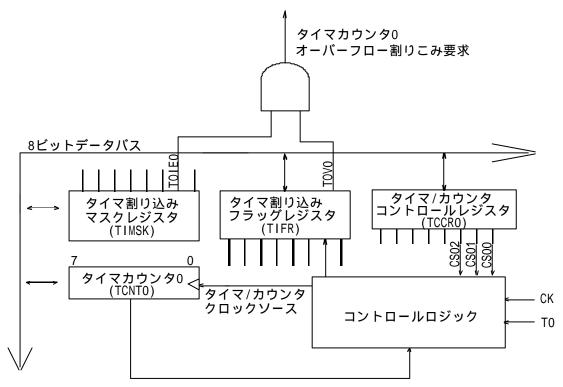

#### タイマ/カウンタ0

AT90S1200 には、汎用 8 ビットタイマカウンタ 0 があります。タイマ/カウンタ 0 は 10 ビット分周タイマから分周します。タイマ/カウンタ 0 は内部クロックベースのタイマまたはカウントをトリガする外部オインと接続したカウンタとしても使うことができます。

### タイマ/カウンタ0分周器

図 18 はタイマカウンタの分周器を示しています。

#### 図 18 タイマカウンタ分周器

4 つの分周選択は: 1/8 CK、1/64 CK、1/256 CK、1/1024 CK で、CK は振動子のクロックになります。タイマカウンタ 0 は CK、外部ソース、STOP がクロック源として選択できます。

図 19 ブロックダイアグラム

8 ビットタイマ/カウンタは CK からクロックソース、分周されたクロック、外部クロック から選択されています。加えて、タイマ/カウンタ 0 コントロールレジスタ TCCRO に指定 された通りに、とめることが出来ます。オーバーフローステータスフラッグは、タイマ/カウンタ割りこみフラッグレジスタ TIFR 中で見られます。

コントロール信号は、タイマ/カウンタ 0 コントロールレジスタ TCCR0 の中にあります。

タイマ/カウンタ 0 の割りこみの有効・無効設定は、タイマ/カウンタ 0 割り込みコントロールレジスタ TIMSK 中に見られます。タイマ/カウンタ 0 が外部的にクロックされている時、外部信号は CPU のオシレータ周波数に同期しています。外部クロックが正しくサンプリングされるようにするために、外部クロック信号変化の最小時間幅は少なくとも内部 CPU 1 クロック分なければなりません。外部信号は内部 CPU クロックの立ち上がりでサンプリングされます。

8 ビットタイマ/カウンタ 0 は、低分周率で使う場合には、高精度、高分解能になります。 同様に、高い分周率での用途では、低いスピードの機能、非周期的な動作に対して正確な 計時機能に有用です。

### タイマ/カウンタ0 コントロールレジスタ TCCRO

| ビット        | 7      | 6      | 5      | 4      | 3      | 2            | 1            | 0             |       |

|------------|--------|--------|--------|--------|--------|--------------|--------------|---------------|-------|

| \$33       | -      | -      | -      | -      | -      | CS02         | CS01         | CS00          | TCCR0 |

| _<br>読み込み・ | 読      | 読      | 読      | 読      | 読      | 読/書          | 読/書          | 読/書           | _     |

| 書きこみ       | (Read) | (Read) | (Read) | (Read) | (Read) | (R ead) /    | (Read) /     | (Read) /      |       |

| 初期値        | 0      | 0      | 0      | 0      | 0      | (Write)<br>O | (Write)<br>O | (W rite)<br>O |       |

**ビット 7~3 Res**: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

**ビット 2,1,0 CS02,CS01,CS00**: クロック選択ビット 2,1,0

表 5 クロック分周選択

| CS02 | CS01 | CS00 | 説明                    |  |

|------|------|------|-----------------------|--|

| 0    | 0    | 0    | ストップ・タイマ/カウンタ0が止まります。 |  |

| 0    | 0    | 1    | СК                    |  |

| 0    | 1    | 0    | CK/8                  |  |

| 0    | 1    | 1    | CK/64                 |  |

| 1    | 0    | 0    | CK/256                |  |

| 1    | 0    | 1    | CK/1024               |  |

| 1    | 1    | 0    | 外部ピンT0立ち下がリエッジ        |  |

| 1    | 1    | 1    | 外部ピンT0立ち上がりエッジ        |  |

停止状態ではタイマ有効・無効機能があります。クロック分周モードではオシレータクロックが直接使われます。外部ピンモードはタイマ/カウンタ 0 用に使われる場合、PD4/(T0)ピンが出力設定になっていても、PB4/(T0)での変化でカウンタが回ります。これにより、カウントの切り替えを行います。

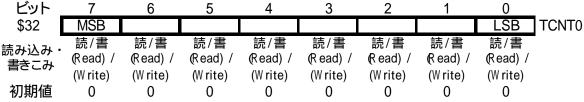

### タイマ/カウンタ 0 TCNTO

タイマ/カウンタ 0 は読み込み・書きこみ可能な数え上げカウンタです。タイマ・カウンタ 0 が書きこまれていて、クロック源がある場合は書きこみ動作に続いて、タイマクロックサイクルでカウントを続けます。

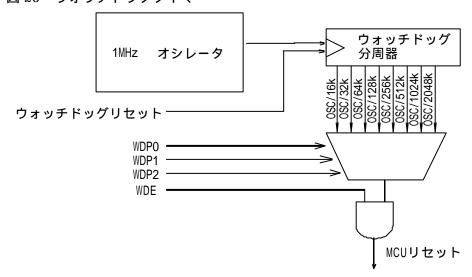

#### ウォッチドッグタイマ

ウォッチドッグタイマは、別の内臓オシレータ(Vcc=5V,1MHz で動く)からクロックされます。他の Vcc レベルの値については特性データを見てください。ウォッチドッグタイマのプリスケーラをコントロールすることによって、ウォッチドッグリセット間隔が調節できます。表 6 を参照してください。

WDR 命令 (ウォッチドッグリセット) はウォッチドッグタイマをリセットします。8 つの クロック周期が選択されると、リセット周期が決定されます。ウォッチドッグリセットな しでリセット周期が過ぎると、AT90S1200 はリセットになり、リセットベクトルから実行 します。ウォッチドッグリセットの計時の詳細については、16 ページを参照してください。

図 20 ウォッチドッグタイマ

ウォッチドッグタイマコントロールレジスタ WDTCR

| ビット        | 7      | 6      | 5      | 4       | 3         | 2         | 1         | 0        | _     |

|------------|--------|--------|--------|---------|-----------|-----------|-----------|----------|-------|

| \$21       | -      | -      | -      | -       | WDE       | WDP2      | WDP1      | WDP0     | WDTCR |

| -<br>読み込み・ | 読      | 読      | 読      | 読       | 読/書       | 読/書       | 読/書       | 読/書      | _     |

| 書きこみ       | (Read) | (Read) | (Read) | (R ead) | (R ead) / | (R ead) / | (R ead) / | (Read) / |       |

|            | ((Caa) | (NCau) | ((Caa) | (( caa) | (W rite)  | (W rite)  | (W rite)  | (W rite) |       |

| 初期値        | 0      | 0      | 0      | 0       | 0         | 0         | 0         | 0        |       |

**ビット7~4 Res**: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に0 として読み込まれます。

ビット3 WDE:ウォッチドッグイネーブル

1. WDE が 1 に設定されて、ウォッチドッグタイマが有効になり、WDE が 0 にクリアされているとウォッチドッグタイマ機能が無効になります。

**ビット2~0 WDP2,WDP1,WDP0**: ウォッチドッグタイマ分周1と0

WDP2,WDP1 と WDP0 ビットは、ウォッチドッグタイマが有効になるとき、ウォッチドッグタイマの分周が決まります。分周値と対応するタイムアウト周期が表 6 に示されています。

|  | 表 6 | ウォッチ | ドッグタイ | イマ分周選択 |

|--|-----|------|-------|--------|

|--|-----|------|-------|--------|

| WDP2 | WDP1 | WDP0 | ウォッチ ドッグ タイマ<br>オシレータサイクル |       | Vcc=5V での 標準<br>タイムアウト |

|------|------|------|---------------------------|-------|------------------------|

| 0    | 0    | 0    | 16kサイクル                   | 47ms  | 15ms                   |

| 0    | 0    | 1    | 32kサイクル                   | 94ms  | 30ms                   |

| 0    | 1    | 0    | 64kサイクル                   | 0.19s | 60ms                   |

| 0    | 1    | 1    | 128kサイクル                  | 0.38s | 0.12s                  |

| 1    | 0    | 0    | 256kサイクル                  | 0.75s | 0.24s                  |

| 1    | 0    | 1    | 512kサイクル                  | 1.5s  | 0.49s                  |

| 1    | 1    | 0    | 1024kサイクル                 | 3.0s  | 0.97s                  |

| 1    | 1    | 1    | 2048kサイクル                 | 6.0s  | 1.9s                   |

注意: ウォッチドッグタイマのオシレータの周波数は、(RC オシレータのため:訳者注) 50 ページの標準特性の節にあるように電圧依存性があります。

WDR (ウォッチドッグリセット)命令はウォッチドッグタイマが有効になる前に常に実行されています。これにより、リセット周期がウォッチドッグタイマの分周設定と確実に一致するようになります。ウォッチドッグタイマがリセットなしに有効になると、ウォッチドッグタイマはゼロからカウントが始まらないことがあります。

### EEPROM 書きこみ・読み込みアクセス

EEPROM アクセスレジスタは I/O 空間でアクセスできます。書き込みアクセス時間は、2.5 ~4ms にわたり、Vcc の電圧に依存しています。しかし、自己計時機能により、次のバイトが書きこまれたときにユーザソフトウェアで検出させます。

EEPROM に書きこむコードがユーザのコードに含まれている場合、いくつか注意しておくべきことがあります。強くフィルタをかけられた電源では、Vcc は電源の上がり下がりに対

してゆっくりと上下します。これにより使われているクロック周期できまる最低電圧より低い値でしばらくの周期動きます。CPU をこの条件を下回って動かすと、プログラムカウンタが意図しないところでジャンプしたり、EEPROM 書きこみコードを実行してしまったりします。EEPROM の統合性を保つため、この場合、外部からしきい値以下の電圧ではリセットする回路を使うようにしてください。

意図せず EEPROM の書きこまれてしまうことを防ぐために、所定の書きこみ手続きに従わなければなりません。これについての詳細は 26 ページの EEPROM コントロールレジスタの説明を参照してください。EEPROM が読み込みまたは書きこまれるとき、CPU は次の命令が実行されるまえに 2 クロックサイクル止まっています。

### EEPROM アドレスレジスタ EEAR

| ビット _      | 7      | 6      | 5        | 4        | 3         | 2        | 1        | 0        |      |

|------------|--------|--------|----------|----------|-----------|----------|----------|----------|------|

| \$1E       | -      | -      | EEAR5    | EEAR4    | EEAR3     | EEAR2    | EEAR1    | EEAR0    | EEAR |

| -<br>読み込み・ | 読      | 読      | 読/書      | 読/書      | 読/書       | 読/書      | 読/書      | 読/書      |      |

| 書きこみ       | (Read) | (Read) | (Read) / | (Read) / | (R ead) / | (Read) / | (Read) / | (Read) / |      |

| EC CV      | ((Caa) | ((Cdd) | (W rite) | (W rite) | (W rite)  | (W rite) | (W rite) | (W rite) |      |

| 初期値        | 0      | 0      | 0        | 0        | 0         | 0        | 0        | 0        |      |

**ビット7 Res**: 予約ビットこのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

### ビット6~0 EEAR6~0: EEPROM アドレス

EEPROM アドレスレジスタ EEAR5  $\sim$  0 は 64 バイト EEPROM 空間中で EEPROM アドレスを指定します。EEPROM データバイトは 0  $\sim$  63 にリニアに割り当てられていきます。

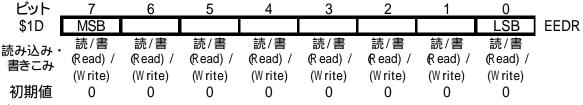

### EEPROM データレジスタ EEDR

ビット7~0 EEDR7~0: EEPROM データ

EEPROM 書きこみ動作に対して、EEDR レジスタは、データを含んでおり、EEAR によって与えられるアドレスに書きこまれます。読込み動作にたいしては、EEPROM から読み出されるデータが含まれており、読み出しアドレスは EEAR で指定されます。

### EEPROM コントロールレジスタ EECR

| ビット                       | 7      | 6      | 5      | 4      | 3      | 2      | 1              | 0              |      |

|---------------------------|--------|--------|--------|--------|--------|--------|----------------|----------------|------|

| \$1C                      | -      | -      | -      | -      | -      | -      | EEWE           | EERE           | EECR |

| -<br>読み込<br>み <b>書</b> きこ | 読      | 読      | 読      | 読      | 読      | 読      | 読/書<br>(Read)/ | 読/書<br>(Read)/ |      |

| み                         | (Read) | (Read) | (Read) | (Read) | (Read) | (Read) | (W rite)       | (W rite)       |      |

| 初期值                       | 0      | 0      | 0      | 0      | 0      | 0      | 0              | 0              |      |

**ビット 7~2** Res: 予約ビットこれらのビットは AT90S1200 の予約ビットで、常に 0 として読み込まれます。

ビット1 EEWE: EEPROM 書きこみイネーブル

EEPROM 書きこみイネーブル信号 EEWE は EEPROM への書きこみストロボになっています。アドレスとデータを正しく設定した時に、EEPROM へ値を書きこむために設定しなければなりません。書き込みアクセス時間 (通常 Vcc=5V で 2.5ms、Vcc=2.7V で 4ms) が過ぎると、EEWE ビットはハードウェアによりクリアされます。ソフト上でこのビットを調べておいて、0 になるのを待って、次のバイトを書きこんで下さい。EEWE が設定されると、CPU は次の命令が実行される前に 2 クロックサイクル停止しています。

### ビット 0 EERE: EEPROM 読み込みイネーブル

EEPROM 読み込みイネーブル信号 EERE は EEPROM への読み込みストロボです。( 訳者注: このビットが 1 になったタイミングで読み込まれ、自動的に 0 に戻されます。ダイナミック。) 正しいアドレスが EEAR レジスタ中で設定されているときに、EERE ビットが設定されなければなりません。EEPROM 読み込みアクセスには 1 命令かかり、EERE ビットを調べておく必要はありません。EERE ビットが設定されると、2 サイクル止まってから次の命令が実行されます。

警告: EEPROM にアクセスしている割りこみルーチンは他の EEPROM アクセスを妨げている場合、割りこまれた EEPROM アクセスがうまくいかなくなるため、EEAR レジスタ、EEDR レジスタが変更されてしまいます。この問題を避けるために、EEPROM の書きこみ動作中はグローバル割りこみのフラッグをクリアしておくことお勧めします。

### EEPROM データ崩壊を防ぐ

Vcc が低くなっている間、供給電源が低すぎるために CPU と EEPROM が正しく動作しない場合があります。この問題は、EEPROM を使った基板レベルのシステムと同じで、同様の設計上の解決策を適用してください。EEPROM のデータ崩壊は電源が低すぎる場合 2 つの状況で起こることがあります。まず、正規に書きこみシーケンスが行われるためには正しく動作するための最低電圧が必要です。次に、CPU は電源電圧が低すぎると、命令を間違って実行してしまうことがあります。

EEPROM データ崩壊は、以下の設計上の忠告に従うことによって簡単に避けることができます。(1つで十分です。)

- 1. AVR のリセットを電源が不充分な間アクティブ(L レベル)にしておいてください。 これは、ブラウンアウト検出器(BOD)としてよく引き合いに出される外部の低 Vcc リセット保護回路により最もうまく行うことができます。パワーオンリセットと低電圧 保護に関する考察するためには、アプリケーションノート AVR180 を参照してください。

- 2. Vcc が低くなっている間に AVR のコアをパワーダウンスリープモードにしておいてください。これにより、CPU が命令の解読・実行を行えなくなり、意図しない書きこみ

から EEPROM を十分に保護することができます。

3. ソフトでメモリ内容を変える機能が必要ではなくても、フラッシュメモリ中に定数を蓄えてください。フラッシュメモリは CPU によって更新され、データ崩壊を受けなくなります。

### アナログコンパレータ

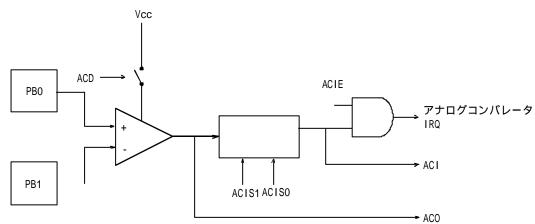

アナログコンパレータは、正入力 PB0(AIN0)と負入力 PB1(AIN1)の入力値を比較します。 正入力ピン PB0(AIN0)の方が負入力ピン PB1(AIN1)より高い場合に、アナログコンパレータ出力 ACO が設定(=1)になります。 コンパレータの出力はアナログコンパレータ割りこみをトリガするために設定されます。 コンパレータ出力の立ち上がり・立ち下がり・トグルでトリガするかを選択できます。 コンパレータのブロックダイアグラムとその周りのロジックに付いては図 21 に示してあります。

### 図 21 アナログコンパレータブロックダイアグラム

アナログコンパレータコントロール・ステータスレジスタ ACSR

| ビット   | 7        | 6       | 5        | 4        | 3        | 2       | 1         | 0        | _    |

|-------|----------|---------|----------|----------|----------|---------|-----------|----------|------|

| \$08  | ACD      |         | ACO      | ACI      | ACIE     | -       | ACIS1     | ACIS0    | ACSR |

| 読み込み・ | 読/書      | 読       | 読/書      | 読/書      | 読/書      | 読       | 読/書       | 読/書      | -    |

| 記の込み・ | (Read) / | (Read)  | (Read) / | (Read) / | (Read) / | (Read)  | (R ead) / | (Read) / |      |

| EC CV | (W rite) | (n eau) | (W rite) | (W rite) | (W rite) | (N eau) | (W rite)  | (W rite) |      |

| 初期值   | 0        | 0       | 0        | 0        | 0        | 0       | 0         | 0        |      |

・ビット7 ACD:アナログコンパレータ無効

このビットが 1 に設定されている時、アナログコンパレータの電源が OFF になります。このビットは、アナログコンパレータを OFF にするためにいつでも使うことができます。これによりアクティブな状態やアイドルモードでの消費電力を減らすことができます。ACD ビットを変えるときは、アナログコンパレータ入力は ACSR 中の ACIE をクリアすることによって無効になります。そうでない場合このビットが変わったときに割り込みが起こります。

・ビット 6 Res: 予約ビット

このビットは AT90S1200 の予約ビットで、常に0 として読み込まれます。

・ビット 5 ACO: アナログコンパレータ出力

ACO はコンパレータ出力と直接つながっています。

・ビット4 ACI:アナログコンパレータ割りこみフラッグ

コンパレータ出力のイベントにより割りこみがトリガさた時、このビットが設定されます。この割りこみモードは、ACSIO と ACIS1 によって定義されます。アナログコンパレータ割りこみルーチンは ACIE が 1 に設定されて、SREG 中の I ビットが 1 に設定された場合、実行されます。ACI は対応する割りこみベクトルが実行されたときにハードウェアによってクリアされます。変わりに論理 1 を書きこむことによってフラッグをクリアすることができます。しかし、SBI、CBI 命令を使ってレジスタ中の他のビットが修正する場合で、動作が起こる前に ACI が設定されてしまった場合、ACI がクリアされます。

・ビット3 ACIE:アナログコンパレータ割りこみイネーブル

ACIE が 1 に設定されていて、ステータスレジスタの I ビットが 1 に設定されている時、アナログコンパレータ割りこみがアクティブになります。クリア (0) にされると、割りこみが無効になります。

・ビット2 Res: 予約ビット

このビットは AT90S1200 の予約ビットで、常に0 として読み込まれます。

・**ビット1、0 ACIS1、ACIS0:アナログコンパレータ**割りこみモード選択 これらのビットによりどのイベントでアナログコンパレータ割りこみをトリガするかを決 めます。表 7 の設定**る**参照してください。

| <b>≠</b> ~  | ACIS1/ACIS0 | ~                                          |

|-------------|-------------|--------------------------------------------|

| <b>=</b> '/ |             | //\=\tau=\tau=\tau=\tau=\tau=\tau=\tau=\ta |

|             |             |                                            |

| ACIS1 | ACIS0 | 割りこみモード               |

|-------|-------|-----------------------|

| 0     | 0     | 出力トグルでのコンパレータ割りこみ     |

| 0     | 1     | 予約                    |

| 1     | 0     | 出力エッジの立ち下がりコンパレータ割りこみ |

| 1     | 1     | 出力エッジの立ち上がリコンパレータ割りこみ |

注意: ACIS1/ACIS0 ビットを変えるとき、アナログコンパレータ割りこみは ACSR レジスタ中のイネーブルビットをクリアすることにより無効にすることができます。そうでない場合、ビットが変わったときに割り込みが起こることがあります。

#### I/O ポート

デジタル I/O ポートとして使われる場合、全 AVR ポートは、読み込み・修正・書きこみ機能を持っています。他のピンの方向を意図せず変えてしまうことなく、1 つのポートピンの方向を、SBI,CBI 命令で変更できることを意味しています。同様に(出力として構成されている場合)ドライブ値の変更、(入力設定の場合)プルアップ抵抗の有効・無効についてもいえます。

### ポートB

AT90S1200 に対してポートBピンは 8 ビット双方向 I/O ポートです。

3 つの I/O メモリアドレスの位置は、それぞれ、データレジスタ PORTB に対しては\$18、データ方向レジスタ DDRB\$17、ポート B 入力ピン PINB は\$16 になります。データレジスタとデータ方向レジスタが読み込み・書きこみができるのに対し、ポート B 入力ピンアドレスは、読み込み専用です。

全ポートピンは個々にプルアップ抵抗を選択可能です。ポートB出力バッファは 20mA まで流し込むことができるので、LED ディスプレイを直接駆動できます。PB0 ~ PB7 は入力として使うことができ、外部的に L レベルにしてあるとき、プルアップ抵抗が有効になると電流を流すことができます。

ポートBピンは次の表に示されているような機能選択ができます。

表8 ポートBピンの選択機能

| ポートピン | 選択機能                     |

|-------|--------------------------|

| PB0   | AINO(アナログコンパレータ正入力)      |

| PB1   | AINO(アナログコンパレータ負入力)      |

| PB5   | MOSI (メモリダウンロード用のデータ入力線) |

| PB6   | MISO (メモリダウンロード用のデータ出力線) |

| PB7   | SCK (シリアルクロック入力 )        |

ピンが選択機能を使うためには、DDRB と PORTB レジスタは、選択機能の説明に従って 設定されなければなりません。

### ポートB データレジスタ PORTB

| ビット       | 7                          | 6                          | 5                          | 4                         | 3                         | 2                         | 1                         | 0                         |       |

|-----------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|-------|

| \$18      | PORTB7                     | PORTB6                     | PORTB5                     | PORTB4                    | PORTB3                    | PORTB2                    | PORTB1                    | PORTB0                    | PORTB |

| 読み込み ききこみ | 読/書<br>(Read) /<br>(Write) | 読/書<br>(Read) /<br>(Write) | 読/書<br>(Read) /<br>(Write) | 読/書<br>(Read)/<br>(Write) | 読/書<br>(Read)/<br>(Write) | 読/書<br>(Read)/<br>(Write) | 読/書<br>(Read)/<br>(Write) | 読/書<br>(Read)/<br>(Write) |       |

| 初期值       | 0                          | 0                          | 0                          | 0                         | 0                         | 0                         | 0                         | 0                         |       |

| ポートB      | 方向レジス                      | タ DDR                      | B                          |                           |                           |                           |                           |                           |       |

| ビット       | 7                          | 6                          | 5                          | 4                         | 3                         | 2                         | 1                         | 0                         |       |

| \$17      | DDB7                       | DDB6                       | DDB5                       | DDB4                      | DDB3                      | DDB2                      | DDB1                      | DDB0                      | DDRB  |

| 読み込み・     | 読/書<br>(Read) /            | 読/書<br>(Read) /            | 読/書<br>(Read) /            | 読/書<br>(Read) /           | 読/書<br>(R ead) /          | 読/書<br>(R ead) /          | 読/書<br>(Read)/            | 読/書<br>(Read) /           | •     |

| 初期值       | (W rite)<br>O              | (W rite)<br>O              | (W rite)<br>0              | (W rite)<br>O             |       |

| ポートB      | 入力アドレ                      | ス PIN                      | В                          |                           |                           |                           |                           |                           |       |

| ビット       | 7                          | 6                          | 5                          | 4                         | 3                         | 2                         | 1                         | 0                         |       |

| \$16      | PINB7                      | PINB6                      | PINB5                      | PINB4                     | PINB3                     | PINB2                     | PINB1                     | PINB0                     | PINB  |

| 読み込み・     | 読                          | 読                          | 読                          | 読                         | 読                         | 読                         | 読                         | 読                         | •     |

| 書きこみ      | (Read)                     | (Read)                     | (R ead)                    | (R ead)                   | (Read)                    | (Read)                    | (Read)                    | (Read)                    |       |

| 初期値       | Hi-Z                       | Hi-Z                       | Hi-Z                       | Hi-Z                      | Hi-Z                      | Hi-Z                      | Hi-Z                      | Hi-Z                      |       |

| ポートB      | 入力ピンア                      | <b>'</b> ドレスは              | PINB は                     | レジスタ                      | ではありま                     | ません。こ                     | のアドレ                      | スでポー                      | ЬB    |

ピンの物理値のアクセスが有効になります。PORTB を読み込むとき、ポート B データラッチが読み込まれ、PINB を読み込むときは、ピン上の物理値が読みこまれます。

### 一般デジタル I/O としてのポート B

ポート B ピンの全部のピンが、デジタル I/O ピンとして使われているとき、同じ機能を持っています。

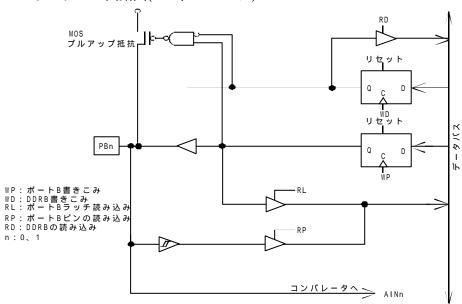

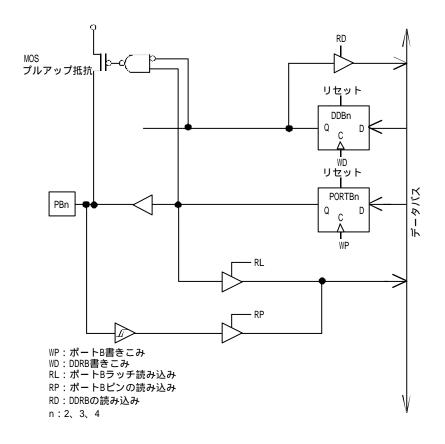

PBn、汎用 I/O ピン: DDRB レジスタ中の DDBn レジスタピンの方向が決まります。 DDBn が 1 に設定されている時、PBn は出力ピンとして構成されます。 DDBn がクリアされている場合、PBn は入力ピンとして構成されます。 入力ピンとして構成されている時で、PORTBn が 1 に設定されている場合 MOS プルアップ抵抗がアクティブになります。 プルアップ抵抗を OFF にするために、PORTB をクリアにするか、出力ピンとして構成してください。 リセット状態がアクティブになったとき、クロックが動いていなくても、トライステートになっています。

表 9 ポートBピンの DDBn の効果

ポート B ピンの選択機能

ポート B ピンの選択機能は:

| DDBn | PORTB | 1/0 | プルアップ抵抗 | コメント                        |

|------|-------|-----|---------|-----------------------------|

| 0    | 0     | 入力  |         | トライステート (ハイインピーダンス状態 )      |

| 0    | 1     | 入力  | ON      | Lレベルにプルダウンされている場合、電流が流れ出ます。 |

| 1    | 0     | 出力  | OFF     | プッシュプルゼロ出力                  |

| 1    | 1     | 出力  | OFF     | プッシュプル1出力                   |

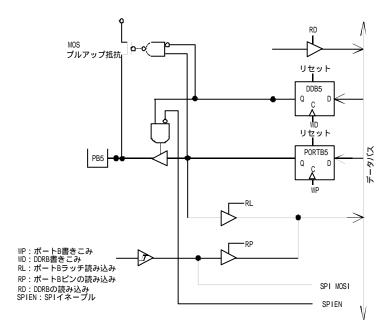

### ・SCK ポートB、ビット7

SCK、メモリの更新・ダウンロード用のクロック入力ピン。

### ・MISO ポートB、ビット6

MISO、メモリの更新・ダウンロード用のデータ出力ピン

・MOSI ポートB、ビット5

MOSI、メモリの更新・ダウンロード用のデータ出力ピン

### ・AIN1 ポートB、ビット1

AIN1、アナログコンパレータ負入力。入力ピンとして構成されている時(DDB1 は 0 にクリアされ、MOS プルアップ抵抗は OFF(PB1 も 0 にクリア)になっています。)、内蔵アナログコンパレータの負入力として働きます。

### ・AINO ポートB、ビットO

AINO、アナログコンパレータ正入力。入力ピンとして構成されている時(DDB0 は 0 にクリアされ、MOS プルアップ抵抗は OFF(PB0 も 0 にクリア)になっています。)、内蔵アナログコンパレータの正入力として働きます。

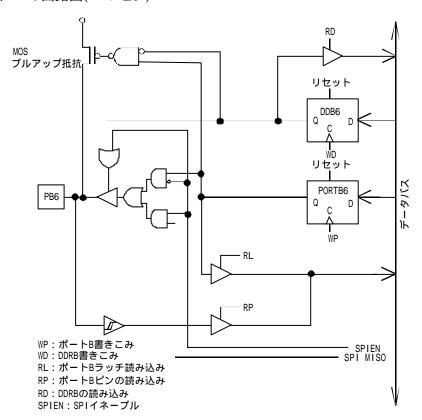

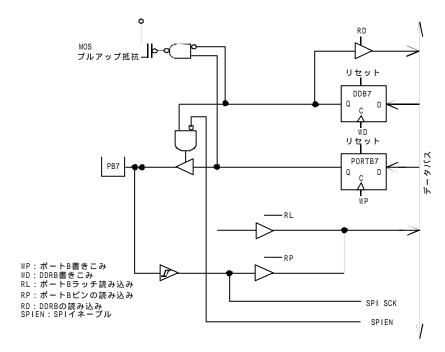

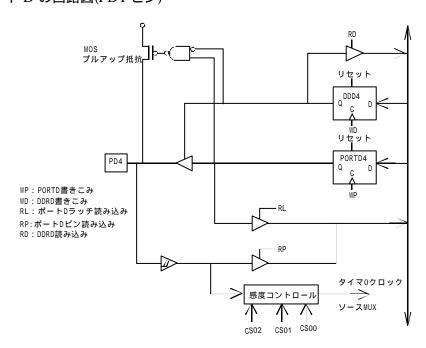

### ポートB の回路図

全ポートが同期していることに注意してください。しかし、同期ラッチはこの図には示されていません。

図 22 ポート B の回路図(PB0、PB1 ピン)

図 23 ポートB の回路図(PB2、PB3 と PB4 ピン)

### 図 24 ポートB の回路図(PB5 ピン)

### 図 25 ポートB の回路図(PB6 ピン)

図 26 ポート B の回路図(PB7 ピン)

### ポートD

3 つの I/O メモリアドレスの位置は、それぞれ、データレジスタ PORTD に対しては\$12、データ方向レジスタ DDRD\$11、ポート D 入力ピン PIND は\$10 になります。データレジスタとデータ方向レジスタが読み込み・書きこみができるのに対し、ポート D 入力ピンアドレスは、読み込み専用です。

ポート D は 7 つの双方向 I/O ピン PD6 ~ PD0 で、内部プルアップ抵抗を持っています。ポート D 出力バッファは 20mA まで流し込むことができます。 $PD0 \sim PD6$  は入力として使うことができ、外部的に L レベルにしてあるとき、プルアップ抵抗が有効になると電流を流すことができます。

ポート D ピンは次の表に示されているような機能選択ができます。

表 10 ポート D ピンの選択機能

| ポートピン | 選択機能               |

|-------|--------------------|

| PD2   | INTO(外部割りこみの要求)    |

| PD4   | T0 (タイマ/カウンタ0外部入力) |

### ポートD データレジスタ PORTD

| ビット   | 7      | 6              | 5               | 4              | 3                | 2              | 1              | 0               |       |

|-------|--------|----------------|-----------------|----------------|------------------|----------------|----------------|-----------------|-------|

| \$12  | -      | PORTD6         | PORTD5          | PORTD4         | PORTD3           | PORTD2         | PORTD1         | PORTD0          | PORTD |

| 読み込み・ | 読      | 読/書<br>(Read)/ | 読/書<br>(Read) / | 読/書<br>(Read)/ | 読/書<br>(R ead) / | 読/書<br>(Read)/ | 読/書<br>(Read)/ | 読/書<br>(Read) / |       |

| 書きこみ  | (Read) | (W rite)       | (W rite)        | (W rite)       | (W rite)         | (W rite)       | (W rite)       | (W rite)        |       |

| 初期値   | 0      | 0              | 0               | 0              | 0                | 0              | 0              | 0               |       |

### ポートD 方向レジスタ DDRD

| ビット _      | 7      | 6       | 5       | 4        | 3        | 2         | 1         | 0        |      |

|------------|--------|---------|---------|----------|----------|-----------|-----------|----------|------|

| \$11       | -      | DDD6    | DDD5    | DDD4     | DDD3     | DDD2      | DDD1      | DDD0     | DDRD |

| -<br>読み込み・ | 読      | 読/書     | 読/書     | 読/書      | 読/書      | 読/書       | 読/書       | 読/書      |      |

| 書きこみ       | (Read) | (Read)  | (R ead) | (Read) / | (Read) / | (R ead) / | (R ead) / | (Read) / |      |

|            | (1000) | (((000) | (1000)  | (W rite) | (W rite) | (W rite)  | (W rite)  | (W rite) |      |

| 初期値        | 0      | 0       | 0       | 0        | 0        | 0         | 0         | 0        |      |

### ポートD 入力アドレス PIND

| ビット               | 7      | 6      | 5       | 4       | 3      | 2      | 1      | 0      |      |

|-------------------|--------|--------|---------|---------|--------|--------|--------|--------|------|

| \$10              | -      | PIND6  | PIND5   | PIND4   | PIND3  | PIND2  | PIND1  | PIND0  | PIND |

| <u>-</u><br>読み込み・ | 読      | 読      | 読       | 読       | 読      | 読      | 読      | 読      | •    |

| 書きこみ              | (Read) | (Read) | (R ead) | (R ead) | (Read) | (Read) | (Read) | (Read) |      |

| 初期值               | 0      | Hi-Z   | Hi-Z    | Hi-Z    | Hi-Z   | Hi-Z   | Hi-Z   | Hi-Z   |      |

ポート D 入力ピンアドレスは PIND はレジスタではありません。このアドレスでポート D ピンの物理値のアクセスが有効になります。PORTD を読み込むとき、ポート D データラッチが読み込まれ、PIND を読み込むときは、ピン上の物理値が読みこまれます。

### 一般デジタル I/O としてのポート D

PDn、汎用 I/O ピン: DDRD レジスタ中の DDDn レジスタピンの方向が決まります。DDDn が 1 に設定されている時、PDn は出力ピンとして構成されます。 DDDn がクリアされている場合、PDn は入力ピンとして構成されます。 入力ピンとして構成されている時で、PORTDn が 1 に設定されている場合 MOS プルアップ抵抗がアクティブになります。 プルアップ抵抗を OFF にするために、PORTD をクリアにするか、出力ピンとして構成してください。 リセット状態がアクティブになったとき、 クロックが動いていなくても、 トライステートになっています。

表 11 ポート D ピンの DDDn の効果

| DDBn | PORTE | 1/0 | プルアップ抵抗 | コメント                        |

|------|-------|-----|---------|-----------------------------|

| 0    | 0     | 入力  | OFF     | トライステート (ハイインピーダンス状態)       |

| 0    | 1     | 入力  | ON      | Lレベルにプルダウンされている場合、電流が流れ出ます。 |

| 1    | 0     | 出力  | OFF     | プッシュプルゼロ出力                  |

| 1    | 1     | 出力  | OFF     | プッシュプル1出力                   |

注意 n:0~6 はピン番号

### ポートD ピンの選択機能

ポート D ピンの選択機能は:

| ポートピ | 選択機能               |

|------|--------------------|

| PD2  | INTO(外部割りこみ0要求)    |

| PD4  | T0 (タイマ/カウンタ0外部入力) |

### ・TO ポートD、ビット4

TO、タイマカウンタのクロックソース。詳しくはタイマの説明を参照してください。

### ・INTO ポートD、ビット2

INTO、外部割りこみソース 0。詳しくはタイマの説明を参照してください。

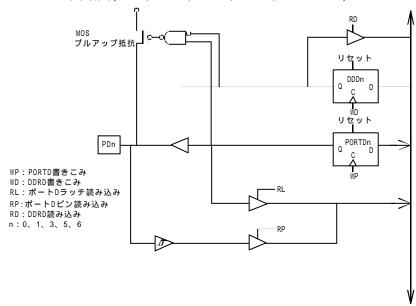

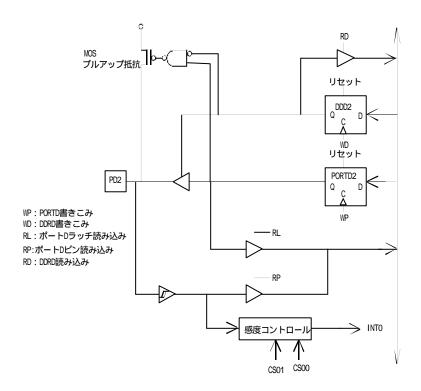

### ポートD の回路図

全ポートが同期していることに注意してください。しかし、同期ラッチはこの図には示されていません。

図 27 ポート D の回路図(PD0、PD1、PD3、PD5、PD6 ピン)

#### 図 28 ポート D の回路図(PD2 ピン)

#### 図 29 ポート D の回路図(PD4 ピン)

#### メモリのプログラミング

#### プログラミングとデータメモリロックビット

AT90S1200 は 2 つのロックビットを持っており、非プログラム「0」 プログラム「1」状態にして表 12 のような特性を得ることができます。ロックビットはチップ消去動作でのみ消去することができます。

表 12 ロックビット保護モード

| メモリ | ロック | ビット |                        |

|-----|-----|-----|------------------------|

| モード | LB1 | LB2 | 保護の種類                  |

| 1   | 1   | 1   | メモリロック機能は有効になっていません    |

| 2   | 0   | 1   | す。                     |

| 3   | 0   | 0   | モード2と同じです。ベリファイもできません。 |

注意:1.パラレルプログラミング(高い電圧)モードにおいて、ヒューズビットを何度もプログラムすると無効になります。ロックビットをプログラムする前にヒューズビットをかけてください。

#### ヒューズビット

AT90S1200は2つのヒューズビット SPIEN と RCEN を持っています。

- ・SPIEN ヒューズがプログラム「0」されている時、シリアルプログラムのデータがダウンロードが有効になります。標準値は「0」です。

- ・RCEN ヒューズがプログラムされるとき、内部 RC オシレータによる MCU のクロック が選択できます。標準値が消去(=1)されます。需要があれば、このビットを非プログラム状態にして届けることができます。

ヒューズビットはシリアルプログラミングはモードではアクセスできません。ヒューズビットの状態はチップ消去の影響は受けません。

#### 署名バイト

全 Atmel マイクロコントローラは 3 バイトの署名バイトを持っており、デバイスの ID として使います。3 つのバイトは、アドレス空間に分かれます。

AT90S1200 に対し、

- 1. \$00: \$1E (Atmel 製品であることを示します。)

- 2. \$01:\$90(1k バイトのフラッシュメモリを示します。)

- 3. \$02:\$01(署名バイト\$01は\$90になっている場合、AT90S1200であることを示します。)

- 1. ロックビットがプログラムされる(ロックモード3)とき、署名バイトは、シリアルプログラミングモードで読み込まれます。署名ビットを読み込むと返ります。: \$00,\$01,\$02

#### フラッシュと EEPROM のプログラミング

Atmel の AT90S1200 には 1k バイトのシステム内蔵プログラム可能フラッシュプログラムメモリと 64 バイトの EEPROM データメモリがあります。

AT90S1200 は内蔵フラッシュプログラムと EEPROM データメモリ消去された状態 (すなわち中身 = \$FF) で並んでおり、プログラムする準備ができています。

デバイスは、高電圧(12V)パラレルプログラミングモードとシリアルプログラミングモード(低い電圧)があります。+12Vはプログラミング有効にするためにだけ使われ、このピンからは重要な電流が流れてくることはありません。シリアルプログラミングモードでは、ユーザのシステム中にあるデバイスへプログラムやデータのダウンロードができます。

AT90S1200 中の EEPROM と PROGRAM メモリはどのプログラミングモードでもバイト ごとにプログラムされます。EEPROM に対して、シリアルプログラミングモード(低い電圧)のセルフタイム書きこみ命令の中で自動消去サイクルが作られます。

プログラミング中に供給電圧は、表 13 と一致していなければなりません。

表 13 プログラミング中の供給電圧

| 型番        | シリアルプログラミング  | パラレルプログラミング |

|-----------|--------------|-------------|

| AT90S1200 | 2.7. ~ 6.0 V | 4.5 ~ 5.5 V |

#### パラレルプログラミング

この節では、AT90S1200 のフラッシュプログラムメモリ、EEPROM データメモリ、ロックビット、ヒューズビットのプログラム・ベリファイの方法を説明しています。

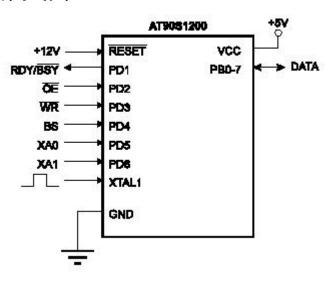

図 30 パラレルプログラミング

#### 信号名

この節では AT90S1200 のいくつかのピンがピンの名前ではなく、パラレルプログラミング中の信号名で説明されています。図 30 と表 14 を参照してください。表 14 に説明されていないピンは、ピン名で参照できます。

XA1/XA ピンで XTAL1 ピンが正のパルスを与えられるときに実行される内容が決まります。

コードについては表 15 を参照してください。

WR と OE にパルスを送ると、ロードされるコマンドで実行内容が決まります。表 16 に示されている機能がそれぞれのビットに割り当てられているバイトがコマンドになります。

表 14 ピン名のマッピング

| プログラミングモードでの信号名 | ピン名     | 入/出力 | 機能                        |

|-----------------|---------|------|---------------------------|

|                 |         |      | 0 :デバイスにプログラミング中 1.デバイスに新 |

| RDY/BSY         | PD1     | 出力   | しいコマンドの準備ができています。         |

| OE              | PD2     | 入力   | 出力有効 (エアクティブ)             |

| WR              | PD3     | 入力   | パルスに書きこみLアクティブ)           |

| BS              | PD4     | 入力   | バイト選択(0で下位バイト 1で上位バイト     |

| XA0             | PD5     | 入力   | XTAL動作ビット0                |

| XA1             | PD6     | 入力   | XTAL動作ビット                 |

| DATA            | PB0 ~ 7 | 入/出力 | 双方向データバス (OEがレベルの時、出力 )   |

表 15 XA1/XA0 のコード

|   |   | XTAL1パルスに対する動作                                         |

|---|---|--------------------------------------------------------|

|   |   | フラッシュ EEPROMア ドレスのロード (フラッシュ用の上下位アドレスバイトはBSによって決まります。) |

| 0 | 0 | アドレスバイトはBSによって決まります。)                                  |

| 0 | 1 | データのロード (フラッシュの上・下位データはBSで決まります                        |

| 1 | 0 | コマンドのロード                                               |

| 1 | 1 | 何も起こりません、アイドル状態                                        |

表 16 コマンドバイトのコード

| コマンドのコー   | 実行されるコマンド        |

|-----------|------------------|

| 1000 0000 | チップ消去            |

| 0100 0000 | ヒューズビットの書きこみ     |

| 0010 0000 | ロックビットの書きこみ      |

| 0001 0000 | フラッシュの書きこみ       |

| 0001 0001 | EEPROMの書きこみ      |

|           | 署名バイトの読み込み       |

| 0000 0100 | ヒューズ・ロックビットの読み込み |

| 0000 0010 | フラッシュの読み込み       |

| 0000 0011 | EEPROMの読み込み      |

#### プログラミングモードに入る

パラレルプログラミングモードで次のアルゴリズムをデバイスに入れてください。

- 1. 表 13 に従って Vcc から GND の間の電源電圧をかけてください。

- 2. RESET とBS ピンを「0」にして、少なくとも100ns待ってください。

- 3. RESET に  $11.5 \sim 12.5$ V をかけてください。12V が RESET に加えられた後、100ns 以内に BS に変化あると、デバイスがプログラミングモードに入ることはできません。

#### チップ消去

チップ消去コマンドはフラッシュとプログラムメモリとロックビットが消去されます。ロックビットは、フラッシュ EEPROM が完全に消去されるまでロックビットはリセットされません。ヒューズビットは変わりません。フラッシュまたは EEPROM が再プログラム

される前にチップ消去が行わなければなりません。

- A: "Chip Erase"のコマンドのロード。

- 1. XA1、XA0を10に設定してください。これによりコマンドのロードが可能になります。

- 2. BS を「0」に設定してください。

- 3. DATA を "1000 0000 " に設定してください。これは、チップ消去のコマンドです。

- 4. XTAL1 に正パルスを与えてください。これでコマンドをロードします。

- 5. WR に twlwh\_ce に負パルスを与えて、Chip Erase を実行できます。 twlwh\_ce は表 17 中にあります。チップ消去は RDY/BSY ピンに変化を起こしません。

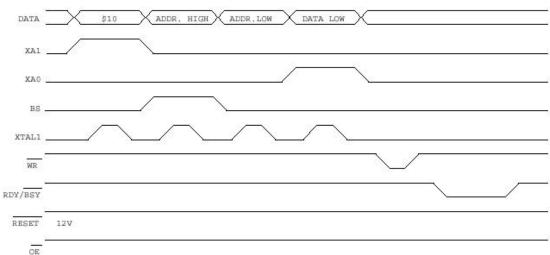

#### フラッシュのプログラミング

- A: 「書きこみフラッシュ」ロードコマンド

- 1. XA1,XA0を10に設定してください。

- 2. BS を「0」に設定して下さい。

- 3. DATA を「0001 0000」に設定して下さい。フラッシュの書きこみのコマンドです。

- 4. XTAL1 に正パルスを与えてください。これでコマンドをロードします。

- B: アドレスの上位バイトのロード

- 1. XA1と XA0を「00」に設定して下さい。

- 2. BS を「1」に設定して下さい。

- 3. DATA=アドレスの下位バイトを(00~FF)に設定して下さい。

- 4. XTAL1 に正パルスを加えてください。これによりアドレスの上位バイトがロードされます。

- C: 下位バイトのアドレスをロード

- 2. BS を「0」に設定して下さい。これにより下位バイトを選択します。

- 3. DATA=データ下位バイト(\$00~\$FF)に設定して下さい。

- 4. XTAL1 に正パルスを与えてください。これによりデータの下位バイトを設定します。

- D: 下位バイトのデータロード

- 1. XA1 と XA0 を「01」に設定して下さい。これで、データがロードされます。

- 2. DATA=データ下位バイトを(\$00~\$FF)に設定して下さい。

- 3. XTAL1 に正パルスを与えてください。これにより、下位バイトデータがロードされます。

- E: 下位データバイトの書きこみ

- 1. BS を 0 に設定して下さい。下位データを選択します

- 2. WR に負パルスを与えてください。これにより、データバイトのプログラミングが始まります。 RDY/BSY は L レベルヘ下がります。

3. RDY/BSY が次のバイトをプログラムするために H レベルにあがるまで待ってください。

(信号波形は図31を参照して下さい。)

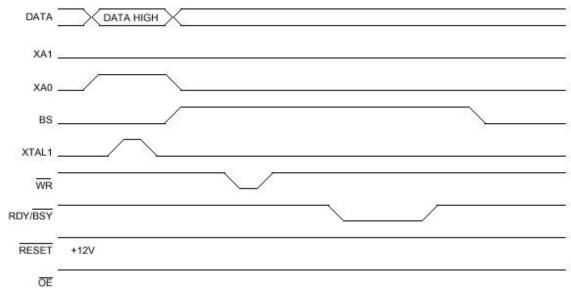

F: H バイトデータのロード

- 1. XA0、XA1 を $\lceil 01

floor$ に設定して下さい。これによりデータロードがイネーブルになります。

- 2. DATA=データ上位バイトを(\$00~\$FF)に設定して下さい。

- 3. XTAL1 に正パルスを与えてください。これで、データの上位バイトがロードされます。

- G:データの上位バイトの書きこみ

- 1. BS を 1 に設定して下さい。これにより上位データが設定されます。

- 2. WR に負パルスを加えてください。これにより、データバイトのプログラミングが始まります。十分なプログラミングを行うために次のことを考えておいてください。

- ・多数のメモリ位置を読み込んだり・書きこむときコマンドは一度だけロードされる必要 があります。

- ・上位バイトのアドレスはフラッシュに新しい 256 ワードのページをプログラムする前に ロードされる必要があります。

- ・データ値に\$FF を書きこまないで下さい。チップ消去の後の全フラッシュと EEPROM の内容になります。これらのことは EEPROM のプログラミング、フラッシュ、EEPROM、署名バイトのよみこみにも適用します。

- 図 31 フラッシュ波形プログラミング

Figure 31. Programming the Flash Waveforms

図 32 フラッシュと波形のプログラミング

#### フラッシュの読み込み

フラッシュメモリを読み込むためのアルゴリズムは次の通りです。(コマンドとアドレスのロードについての詳しいことはフラッシュのプログラミングを参照して下さい。)

- 1. A:「0000 0010」ロードコマンド

- 2. B:上位バイトのアドレスのロード(\$00~\$01)

- 3. C: 下位バイトアドレスのロード(\$00~\$FF)

- 4. OE を 0 に設定、BS を 0 に設定して下さい。下位アドレスのフラッシュは DATA で読むことができます。

- 5. BS を「1」に設定して下さい。上位バイトのフラッシュワードは DATA から読み込む ことができます。

- 6. OE を 1 に設定して下さい。

#### EEPROM のプログラミング

EEPROM データのプログラミングアルゴリズムは次の通りです。(アドレスとデータのロードコマンドの詳しいことはフラッシュのプログラミングを参照してださい。)

- 1. A:ロードコマンド「0001 0001」

- 2. C: 下位バイトアドレス(\$00~\$3F)のロード

- 3. D: データ下位バイト(\$00~\$FF)のロード

- 4. E: データ下位バイトの書きこみ。

#### EEPROM の読み込み

EEPROM メモリを読み込むためのアルゴリズムは次の通りです。(コマンドとアドレスの

ロードについての詳細は、フラッシュのプログラミングを参照して下さい。)

- 1. A:「0000 0011」ロードコマンド

- 2. C: 下位バイトのアドレス(\$00~\$3F)のロード

- 3. OE 設定を「0」に、BS を「0」の設定して下さい。EEPROM データは DATA に読み込むことができます。

- 4. OE を 1 に設定して下さい。

#### ヒューズピットのプログラミング

ヒューズビットのプログラミングのアルゴリズムは次の通りです。(コマンドとロードのプログラミングの詳細はフラッシュのプログラミングを参照して下さい。)

- 1. A:「0100 0000」のロードコマンド

- 2. B: データ下位バイトのロード。 ビット n=0 でヒューズビットがプログラムになります。 ビット 5=SPIEN ヒューズ

ビット 0=RCEN ヒューズ

ビット  $7 \sim 6$ 、 $4 \sim 1 = 1$ 。これらのビットは予約されており、非プログラム状態「1」にしておかなければなりません。

3. WR は  $t_{WLWH\_PFB}$  の時間幅を持つ負パルスを与えて、プログラムを実行して下さい。  $t_{WLWH\_PFB}$  は表 17 にあります。ヒューズビットをプログラミングしても、RDY/BSY ピンでは何も起こりません。

#### ロックピットのプログラミング

ロックビットのプログラミングのアルゴリズムは次の通りです。(コマンドとデータのローードの詳細に付いてはフラッシュのプログラミングを参照して下さい。)

- 1. A:「0010 0000」ロードコマンド

- 2. D: データ下位バイトのロード。ビット n=0 でロックビットをプログラムします。 ビット 2=ロックビット 2

ビット 1=ロックビット 1

ビット 7~3、0=1、これらのビットは予約されており、非プログラム状態「1」にしておいてください。

3. E:データ下位バイトの書きこみ。

ロックビットはチップ消去を実行することのみによりクリアされます。

#### ヒューズとロックビットの読み込み

ヒューズとロックビットを読み込むためのアルゴリズムは次の通りです。(コマンドとデータのロードの詳細に付いてはフラッシュのプログラミングを参照して下さい。)

1. A:「0000 0100」ロードコマンド

2. OE を 0 に、BS を 1 に設定して下さい。ヒューズとロックビットの状態は、DATA で読み取ることができます。(「0」はプログラムされている状態を意味します。)

ビット 7=ロックビット 1

ビット 6=ロックビット 2

ビット 5=SPIEN ヒューズ

ビット 0=RCEN ヒューズ

3. OE を 1 に設定して下さい。

特に、BSが1に設定される必要があることを特に注意して下さい。

#### 署名バイトの読み込み

署名バイトの読み込みのアルゴリズムは次の通りです。(コマンドとデータのロードの詳細に付いてはフラッシュのプログラミングを参照して下さい。)

- 1. A:「0000 1000」ロードコマンド

- 2. C: 下位バイトアドレス(\$00~\$02)のロード

OE を 0 に、BS を 0 に設定して下さい。選択された署名バイトは、DATA で読み込まれます。

3. OE を 1 に設定して下さい。

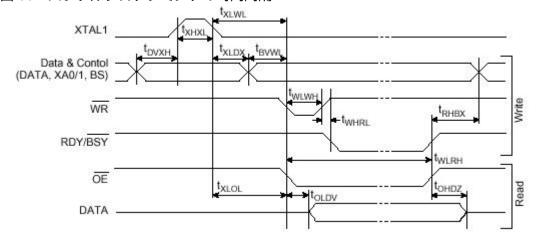

図 33 パラレルプログラミングの時間間隔

|      | D     | ¥33.553 |       | -        |        | T              | - 6 |

|------|-------|---------|-------|----------|--------|----------------|-----|

|      | -     | -       |       |          |        |                |     |

| 表 17 | ハフレル、 | ノロクフミン  | ノクの特性 | $T_A=25$ | ± 10%、 | $Vcc=5V \pm 1$ | 0%  |

| Symbol                | Parameter                                           | Min  | Тур | Max  | Units |

|-----------------------|-----------------------------------------------------|------|-----|------|-------|

| V <sub>PP</sub>       | Programming Enable Voltage                          | 11.5 |     | 12.5 | V     |

| I <sub>pp</sub>       | Programming Enable Current                          |      |     | 250  | μА    |

| t <sub>DVXH</sub>     | Data and Control Setup before XTAL1 High            | 67   |     |      | ns    |

| t <sub>XHXL</sub>     | XTAL1 Pulse Width High                              | 67   | v   |      | ns    |

| t <sub>XLDX</sub>     | Data and Control Hold after XTAL1 Low               | 67   |     |      | ns    |

| t <sub>XLWL</sub>     | XTAL1 Low to WR Low                                 | 67   |     |      | ns    |

| t <sub>BVWL</sub>     | BS Valid to WR Low                                  | 67   |     |      | ns    |

| t <sub>RHBX</sub>     | BS Hold after RDY/BSY High                          | 67   | X.  |      | ns    |

| t <sub>WLWH</sub>     | WR Pulse Width Low <sup>(1)</sup>                   | 67   |     |      | ns    |

| t <sub>WHRL</sub>     | WR High to RDY/BSY Low <sup>(2)</sup>               |      | 20  |      | ns    |

| t <sub>WLRH</sub>     | WR Low to RDY/BSY High <sup>(2)</sup>               | 0.5  | 0.7 | 0.9  | ms    |

| t <sub>XLOL</sub>     | XTAL1 Low to OE Low                                 | 67   |     |      | ns    |

| t <sub>OLDV</sub>     | OE Low to DATA Valid                                |      | 20  |      | ns    |

| t <sub>OHDZ</sub>     | OE High to DATA Tri-stated                          | 9    |     | 20   | ns    |

| t <sub>WLWH_CE</sub>  | WR Pulse Width Low for Chip Erase                   | 5    | 10  | 15   | ms    |

| t <sub>WLWH_PFB</sub> | WR Pulse Width Low for Programming the Fuse<br>Bits | 1.0  | 1.5 | 1.8  | ms    |

- 注意 1. twlwh\_ce はチップ消去用で twlwh\_pfBはヒューズビットのプログラミング用です。

- 2.  $t_{WLWH}$ は  $t_{WLRH}$ よりも長く保たれていると、RDY/BSY パルスが見られることはありません。

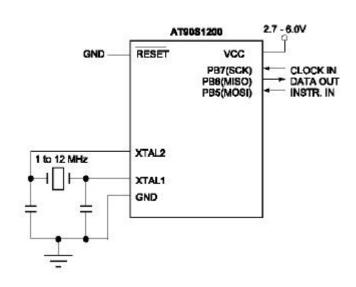

#### シリアルダウンロード

プログラムデータとメモリ配列は RESET がグランドに落ちている間、SPI を使ってプログラムすることができます。シリアルインターフェイスは SCK、MOSI(入力)、MISO (出力)ピンからなります。図 34 を参照してください。RESET が L レベルになったあと、プログラミングイネーブル命令は、プログラム/消去命令が実行されるまでに、最初に実行しておく必要があります。

図 34 シリアルプログラミングとベリファイ

EEPROM では、自動消去サイクルがセルフタイマの書きこみ命令で作られるので、最初にチップ消去命令を行う必要はありません。チップ消去命令は、プログラムと EEPROM 配列中のすべてのメモリ位置の内容がすべてSFF に変わります。

プログラムと EEPROM メモリ配列は別々のアドレス空間を持っており、フラッシュメモリは $\$0000 \sim \$01$ FF、EEPROM データメモリでは $\$000 \sim \$03$ F まであります。

外部クロックを XTAL1 ピンに加えるか、水晶を XTAL1 と XTAL2 をはさんで接続しておく必要があります。シリアルクロック入力のための L レベルと H レベルの最小周期が次のように定義されます。

L レベル: 1 XTAL 1 クロックサイクル

H レベル: 4 XTAL 1 クロックサイクル

#### シリアルプログラミングのアルゴリズム

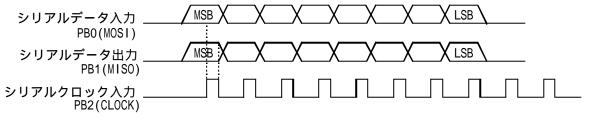

シリアルデータを AT90S1200 を書きこむとき、データは SCK の立ち上がりエッジでクロックされます。

AT90S1200 から読み込むとき、データは SCK の立ち下がりでクロックされます。タイミングの詳細は、図 35、図 36、表 20 を参照してください。

シリアルプログラミングモードにおいて、AT90S1200 をプログラム・ベリファイするためには、次のシーケンスを推奨しています。(表 17 の 4 バイト命令の形式を参照してください。)

#### 1. パワーアップシーケンス

RESET と SCK が 0 に設定されている場合、Vcc と GND の間に電源を加えてください。 XTAL1 と XTAL2 に水晶がつながっていない場合、または内部 RC オシレータからデバイスが駆動されていない場合、XTAL1 ピンにクロック信号を与えてください。パワーアップの間 SCK が L レベルになっている保証がない場合、RESET ピンを SCK が 0 に設定しててから、正パルスを RESET に与えてください。

- 2. 最低 20ms 待って、MOSI (PB5) ピンヘプログラムイネーブル命令を送ることによってシリアルプログラミングが有効になります。

- 3. チップ消去プログラムが実行される(フラッシュを消去するのになされなければなりません。) 場合、命令後時間  $t_{WD\_ERASE}$  だけ待って、RESET に正パルスを与えてください。 ステップ 2 から始めてください。 $t_{WD\_ERASE}$  の値のに付いては 49 の表 21 をを参照して下さい。

- 4. フラッシュまたは EEPROM 配列は一度に 1 バイトごとプログラムされ、アドレスとデータを適当な書きこみ命令でと緒に出します。EEPROM メモリ位置は、新しくデータが書きこまれる前に最初に自動消去されます。送信命令の後、twp\_prog 待ってください。消去されたデバイスでは、データファイル中の\$FF はプログラムしておく必要があります。twp\_progの値に付いては 49 の表 22 を参照して下さい。

- 5. 読み込み命令を使って、どんなメモリの位置でもベリファイできます。シリアル出力 MISO(PB6)ピンに選択されたアドレスの定数を返します。プログラムの最後で通常動作 を行わせるために RESET を H レベルにしておくことができます。

- 6. パワーオフシーケンス(必要な場合)

XTAL1 を 0 に設定してください。(水晶が使われていない場合または内蔵 RC オシレータ から動いている場合)

RESET を 1 に設定して下さい。

Vcc を OFF にしてください。

#### EEPROM データポーリング

1 バイトが EEPROM ヘプログラムされる場合、プログラムされているアドレスを読み込んでいる間は、自動消去が終わるまで P1 の値になり、そのあと P2 の値になります。P1 と P2 の値については、表 18 を参照してください。

デバイスが新しい EEPROM バイトに対して準備ができている時には、プログラム値が正しく読み込まれます。これは、いつ次のバイトを書きこむことができるかを決めるために使います。これは P1 と P2 の値には作用しないため、これらの値をプログラムするときは、次のバイトをプログラムする前に、少なくとも規定の時間 twp\_prog だけ待たなければいけません。twp\_prog の値については表 22 を参照してください。チップ消去されたデバイスは全ロケーションでSFF になっているので、SFF を含んでいるアドレスのプログラミングはスキップされます。最初にチップ消去されたデバイス以外では EEPROM が再プログラムされてもこれは、適用されません。

#### フラッシュのデータポーリング

フラッシュにバイトがプログラムされている場合、プログラムされているアドレスを読み込むとSFF になります。デバイスが新しい EEPROM バイトに対して準備ができている時には、プログラム値が正しく読み込まれます。これは、いつ次のバイトを書きこむことができるかを決めるために使います。これは値SFF に対しては作用しないため、これらの値をプログラムするときは、次のバイトをプログラムするまで、少なくとも規定の時間 twp\_progだけ待たなければいけません。チップ消去されたデバイスは全ロケーションでSFF になっているので、SFF を含んでいるアドレスのプログラミングはスキップされます。これは、最初にチップ消去をせずに EEPROM を再プログラムした場合当てはまりません。

表 18 EEPROM ポーリング中の読み返し値

| The state of the s | - (No.) (Mo.) |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

| Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P1            | P2   |

| AT90S1200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | \$00          | \$FF |

#### 図 35 シリアルプログラミング波形

表 19 AT90S1200 のシリアルプログラミング命令

|                         | Instruction Format |           |                   |           |                                                                      |  |

|-------------------------|--------------------|-----------|-------------------|-----------|----------------------------------------------------------------------|--|

| Instruction             | Byte 1             | Byte 2    | Byte 3            | Byte4     | Operation                                                            |  |

| Programming<br>Enable   | 1010 1100          | 0101 0011 | XXXX XXXX         | XXXX XXXX | Enable Serial Programming while RESET is low.                        |  |

| Chip Erase              | 1010 1100          | 100x xxxx | XXXX XXXX         | XXXX XXXX | Chip Erase both Flash and EEPROM memory arrays.                      |  |

| Read Program<br>Memory  | 0010 <b>H</b> 000  | 0000 000a | bbbb bbbb         | 0000 0000 | Read H (high or low) byte o from Program memory at word address a:b. |  |

| Write Program<br>Memory | 0100 <b>H</b> 000  | 0000 000a | bbbb bbbb         | 1111 1111 | Write H (high or low) byte i to Program memory at word address a:b.  |  |

| Read EEPROM<br>Memory   | 1010 0000          | 0000 0000 | 00bb bbbb         | 0000 0000 | Read data o from EEPROM memory at address b.                         |  |

| Write EEPROM<br>Memory  | 1100 0000          | 0000 0000 | 00bb bbbb         | 1111 1111 | Write data I to EEPROM memory at address b.                          |  |

| Write Lock Bits         | 1010 1100          | 1111 1211 | XXXX XXXX         | XXXX XXXX | Write Lock bits. Set bits 1,2='0' to program Lock bits.              |  |

| Read Signature<br>Byte  | 0011 0000          | XXXX XXXX | хххх хх <b>ьь</b> | 0000 0000 | Read Signature byte o from address b.(1)                             |  |

#### 注意 a=上位ビットアドレス

b=下位ビットアドレス

H=0 下位バイト、1 上位バイト

o=データ出力

i=データ入力

×=値に依存しない

1=ロックビット1

2=ロックビット2

注意 1.署名バイトはロックモード 3 すなわち両ロックビットがプログラムされている 時、読み込むことができません。

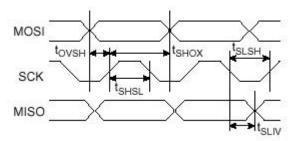

#### シリアルプログラミングの特性

図 36 シリアルプログラミングとベリファイ

#### 表 20 低電圧シリアルプログラミングの特性

T<sub>A</sub>=-40 ~85 、Vcc=2.7~6.0V(とくに断りがない場合)

| Symbol              | Parameter                                           | Min                    | Тур | Max | Units |

|---------------------|-----------------------------------------------------|------------------------|-----|-----|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency (V <sub>CC</sub> = 2.7 - 4.0V) | 0                      |     | 4   | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period (V <sub>CC</sub> = 2.7 - 4.0V)    | 250                    |     |     | ns    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency (V <sub>CC</sub> = 4.0 - 6.0V) | 0                      |     | 12  | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period (V <sub>CC</sub> = 4.0 - 6.0V)    | 83.3                   |     |     | ns    |

| t <sub>SHSL</sub>   | SCK Pulse Width High                                | 4 t <sub>CLCL</sub>    | 33  |     | ns    |

| t <sub>SLSH</sub>   | SCK Pulse Width Low                                 | taca                   |     |     | ns    |

| tovsh               | MOSI Setup to SCK High                              | 1.25 t <sub>CLCL</sub> |     |     | ns    |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High                            | 2.5 t <sub>CLCL</sub>  |     |     | ns    |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid                               | 10                     | 16  | 32  | ns    |

#### 表 21 チップ消去命令の後の最小待ち時間

| 記号                    | 3.2V | 3.6V | 4.0V | 5.0V |

|-----------------------|------|------|------|------|

| t <sub>WD_ERASE</sub> | 18ms | 14ms | 12ms | 8ms  |

#### 表 22 フラッシュか EEPROM に書きこんだ後の最小待ち時間

| 記号                   | 3.2V | 3.6V | 4.0V | 5.0V |

|----------------------|------|------|------|------|

| t <sub>WD_PROG</sub> | 9ms  | 7ms  | 6ms  | 4ms  |

#### 電気的特性

#### 最大定格

| 動作温度                    | -55 ~ +125       |

|-------------------------|------------------|

| 耐久温度                    | -65 ~ +150       |

| RESET端子以外の<br>GNDに対する電圧 | -1.0V ~ Vcc+0.5V |

| RESET端子の<br>GNDに対する電圧   | -1.0V~+13.0V     |

| 最大動作電圧                  | 6.6V             |

| I/0ピン1本あたりの直流電流         | 40.0mA           |

| VccとGNDピンの直流電流          | 200.0mA          |

|                         |                  |

注意:最大定格を超える値を加えると、デバイスに致命的な損傷を与えることがあります。この定格は、内部破壊のおこる定格であって、この値での動作を保証するものではありません。この仕様の動作の節に示されている値を超える他の条件でデバイスが動作することは保証していません。最大定格に長くさらされると、デバイスの信頼性に影響を与えることがあります。

**DC 特性** T<sub>A</sub>=-40 ~85 、Vcc=2.7~6.0V(とくに断りがない場合)

| 記号                | パラメータ                   | 条件                             | 最小値     | 標準値 | 最大値                   | 単位 |

|-------------------|-------------------------|--------------------------------|---------|-----|-----------------------|----|

| $V_{IL}$          | Lレベル入力電圧                | (XTALピンを除く)                    | -0.5    |     | 0.3Vcc <sup>(1)</sup> | V  |

| $V_{IL1}$         | Lレベル入力電圧                | XTALピン                         | -0.5    |     | 0.1 <sup>(2)</sup>    | V  |

| $V_{IH}$          | Hレベル入力電圧                | (XTAL,RESETを除く)                | 0.6Vcc  |     | Vcc+0.5               | V  |

| V <sub>IH1</sub>  | Hレベル入力電圧                | XTALピン                         | 0.7Vcc  |     | Vcc+0.5               | V  |

| $V_{IH2}$         | Hレベル入力電圧                | RESETピン                        | 0.85Vcc |     | Vcc+0.5               | V  |

| $V_{OL}$          | PORTB出力Lレベル電圧           | I <sub>OL</sub> =20mA,Vcc=5V   |         |     | 0.6                   | V  |

|                   |                         | I <sub>OL</sub> =10mA,Vcc=3V   |         |     | 0.5                   | V  |

| $V_{OH}$          | PORTB出力Hレベル電圧           | I <sub>OH</sub> =-3mA,Vcc=5V   | 4.3     |     |                       | V  |

|                   |                         | I <sub>OH</sub> =-1.5mA,Vcc=3V | 2.3     |     |                       | V  |

| I <sub>IL</sub>   | I/Oピンの入力漏れ電流            | Vcc=6V,Lレベルのピン(絶対値)            |         |     | 8.0                   | μA |

| I <sub>IH</sub>   | I/Oピンの入力漏れ電流            | Vcc=6V,Hレベルのピン(絶対値)            |         |     | 980                   | nA |

| RRST              | リセットのプルアップ抵抗            |                                | 100     |     | 500                   | k  |

| R <sub>I/O</sub>  | I/Oピンののプルアップ抵           |                                | 35      |     | 120                   | k  |

| lcc               | AT90S2343の電源電流          | 4MHzで動作、Vcc=3V                 |         |     | 3.0                   | mΑ |

|                   |                         | アイドルモード、Voo=3V、4MHz            |         |     | 3.0                   | mΑ |

| lcc               | パワーダウンモード <sup>5)</sup> | Vcc=3V、WDT有効                   |         | 9   | 15.0                  | μA |

|                   |                         | Vcc=3V、WDT無効                   |         | <1  | 2.0                   | μА |

| V <sub>ACIO</sub> | アナログコンパレータ入力<br>オフセット電圧 | Vcc=5V                         |         |     | 40                    | mV |

| I <sub>ACLK</sub> | アナログコンパレータ入力<br>漏れ電流    | Vcc=5V、Vin=Vcc/2               | -50     |     | 50                    | nA |

| t <sub>ACPD</sub> | アナログコンパレータ進行            | Vcc=2.7                        |         | 750 |                       | ns |

|                   | ディレイ                    | Vcc=4.0V                       |         | 500 |                       | ns |

- 1. 「最大」とは、ピンが L レベルとして読み込まれる保証のある値で最高の値のことです。

- 2. 「最小」とは、ピンが H レベルとして読み込まれる保証がある値で最高の値のことです。

- 3. それぞれの I/O ポートは条件より(Vcc=5V で 20mA、Vcc=3V で 10mA)の定常な条件のもとで、多く流し込むことができますが、次のことに注意しなければなりません。

- 1] I<sub>OL</sub>の和はポートに対して、200mA を越えてはいけません。

- $2| II_{OL}$  の和はポート D0 ~ D5 と XTAL2 に対して 100mA を越えてはいけません。

- 3] I<sub>OL</sub>の和は B0~B7、D6 に対しては 100mA を越えてはいけません。

- $I_{OL}$ がテスト条件を越えた場合、 $V_{OL}$ が仕様を超えることがあります。ピンが表のテスト条件より大きな電流をシンクする保証はありません。

- 4. それぞれの I/O ポートは (Vcc=5V で 20mA、Vcc=3V で 10mA) の定常な条件のもとで、テスト条件以上流し出すことができますが、次のことを注意しなければなりません。

- 1] I<sub>OH</sub>の和はポートに対して、200mA を越えてはいけません。

- 2]  $II_{OH}$ の和はポート  $D0 \sim D5$  と XTAL2 に対して 100mA を越えてはいけません。

- 3] I<sub>OH</sub>の和は B0~B7、D6 に対しては 100mA を越えてはいけません。

- IOHがテスト条件を越えた場合、VOHが仕様を超えることがあります。ピンが表のテスト条件より大きな電流を流し出せる保証はありません。

- 5. パワーダウンでは最小 Vcc は 2V です。

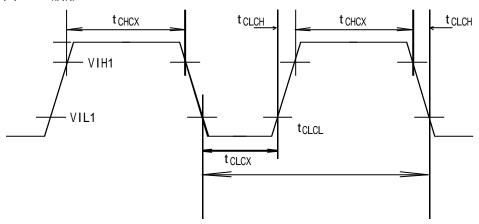

#### 外部クロック駆動波形

図 38 波形

#### 外部クロックの駆動

$T_A = -40 \sim 85$

| 記号                  | パラメータ    | Vcc:2.7 ~ 4.0V |     | Vcc:4.0 ~ 6.0V |     | 単位  |

|---------------------|----------|----------------|-----|----------------|-----|-----|

|                     |          | 最小値            | 最大値 | 最小值            | 最大値 |     |

| 1/t <sub>CLCL</sub> | 振動周波数    | 0              | 4   | 0              | 12  | MHz |

| t <sub>CLCL</sub>   | クロック周期   | 250            |     | 83.3           |     | ns  |

| t <sub>CHCX</sub>   | H レベルの時間 | 100            |     | 33.3           |     | ns  |

| t <sub>CLCX</sub>   | L レベルの時間 | 100            |     | 33.3           |     | ns  |

| t <sub>CLCH</sub>   | 立ち上がり時間  |                | 1.6 |                | 0.5 | μs  |

| t <sub>CHCL</sub>   | 立ち下がり時間  |                | 1.6 |                | 0.5 | μs  |

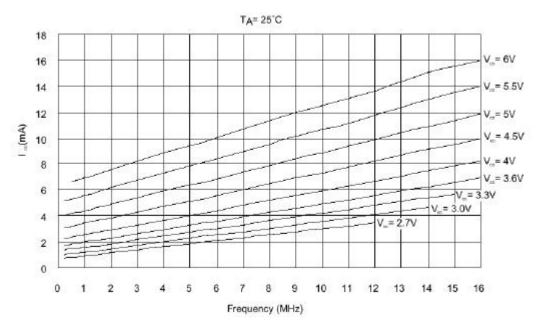

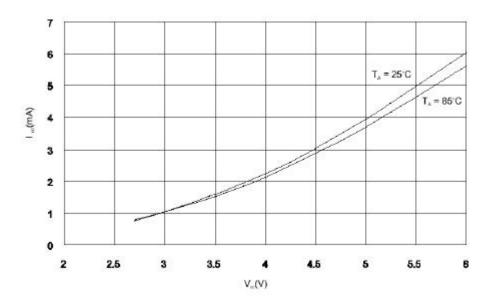

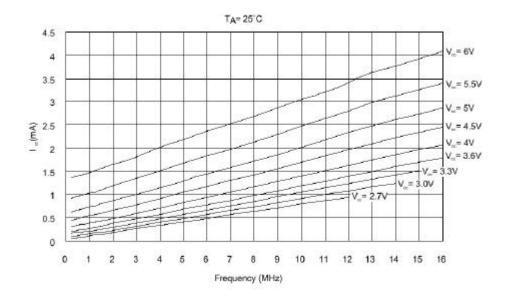

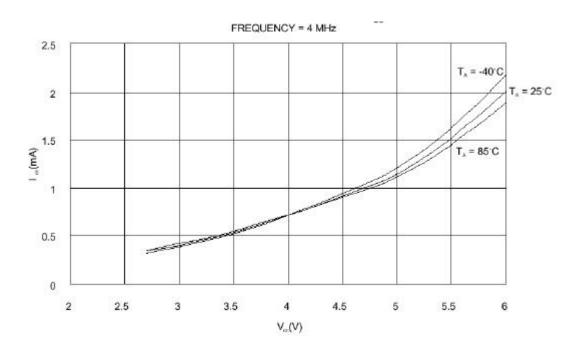

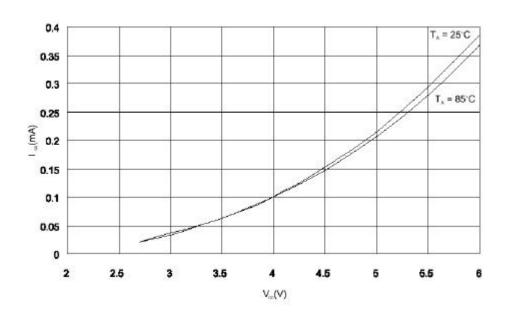

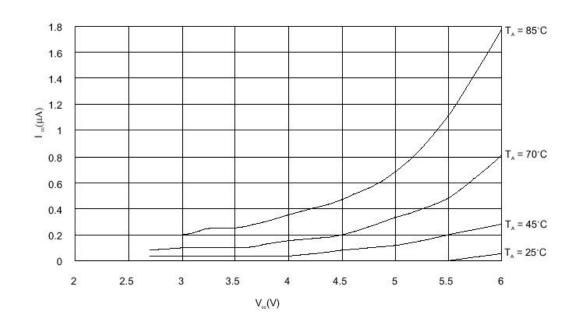

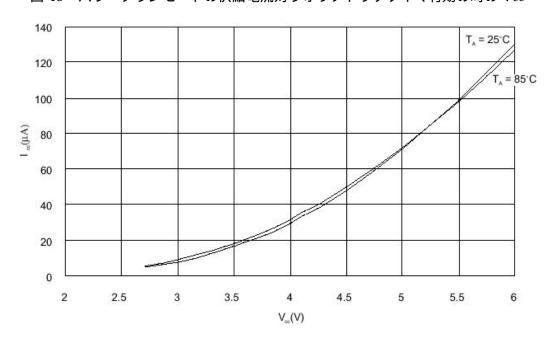

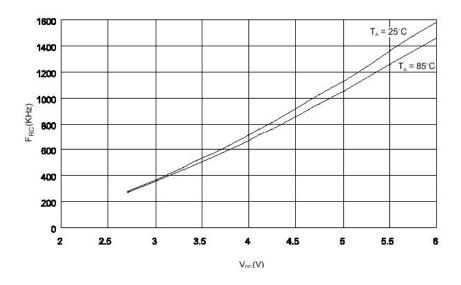

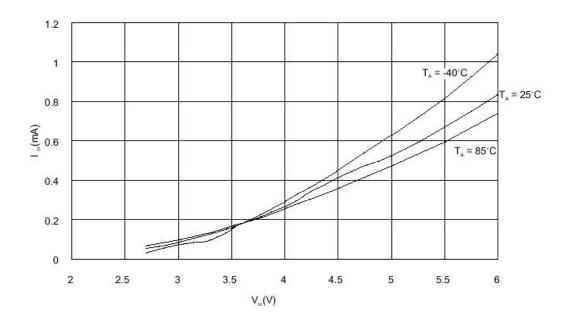

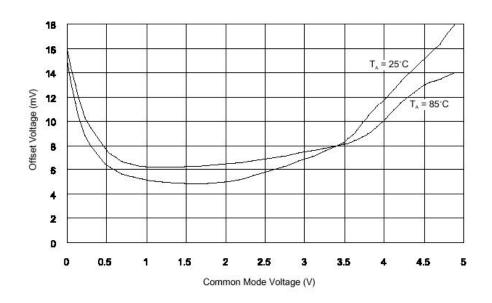

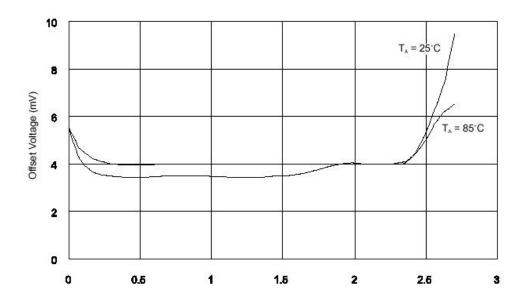

#### 標準的な特性

次の表は標準的な振る舞いを示します。これらのデータは特徴を表していますが、試してあるものはありません。全電流消費の測定は、全 I/O ピンが入力として構成されていて、内部プルアップ抵抗を有効にした状態で行われています。レール トゥ レールの正弦波生成器がクロック源として使われています。

パワーダウンモードの消費電力はクロックの選択とは独立しています。

電流の消費量は、いろいろな要素の関数になっています。例えば、動作電圧、動作周波数、I/O ピンの負荷、I/O ピンの切り替え率、実行コード、周囲温度です。主な要素は、動作電圧と周波数です。

容量負荷からのピンから引き出される電流は、一つのピンに対して  $C_L*Vcc*f$  として見積もることができます。 $C_L$ =容量負荷、Vcc=動作電圧、f=I/O ピンの平均スイッチング周波数です。部品はテスト限界より高い周波数で代表させてあります。部品は、命令コードが示すより高い値では正常に動きません。

ウォッチドッグタイマが有効になったパワーダウンモードとウォッチドッグ無効のパワー ダウンモードの電流消費の差はウォッチドッグタイマの分を引いた差の電流になります。

図38 アクティブ時の供給電流 Icc と周波数

図 39 アクティブ時の供給電流と Vcc

図 40 アクティブ時の供給電流対内部オシレータで駆動しているデバイスの Vcc

図 41 アイドルモード時の供給電流対周波数

図 42 アイドルモード時の供給電流対 Vcc

図 43 アイドル供給電流対内部オシレータ駆動のデバイスの Vcc

図 44 パワーダーウンモード時の供給電流対ウォッチドッグタイマ無効の時の Vcc

図 45 パワーダウンモードの供給電流対ウォッチドッグタイマ有効の時の Vcc

図 46 内蔵 RC オシレータの周波数対 Vcc

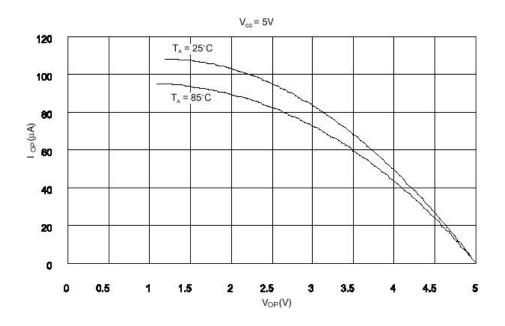

図 47 アナログコンパレータ電流対 Vcc

アナログコンパレータオフセットはオフセットの絶対値として測定されています。

図 48 アナログコンパレータオフセット電圧対コモンモード電圧 Vcc=5V

図 49 アナログコンパレータオフセット電圧対コモンモード電圧 Vcc=2.7V

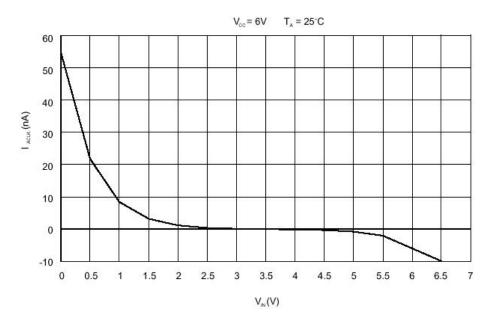

図 50 アナログコンパレータ入力漏れ電流

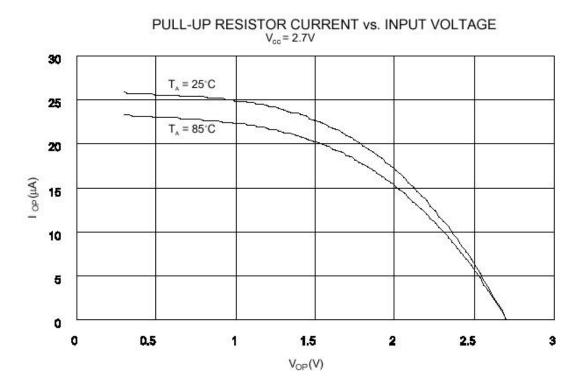

I/O ポートのシンク・ソース容量は1回でピン1本について測定しています。 図 51 プルアップ抵抗電流対入力電圧

図 52 プルアップ抵抗電流対入力電圧

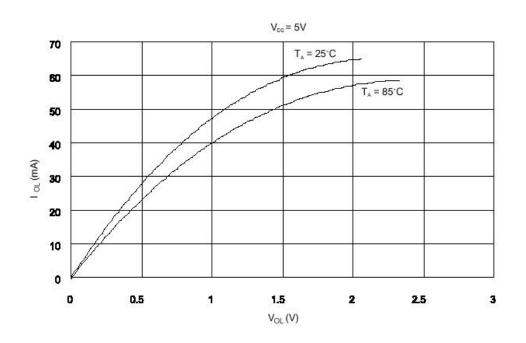

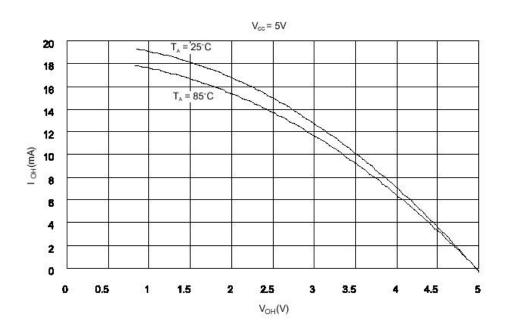

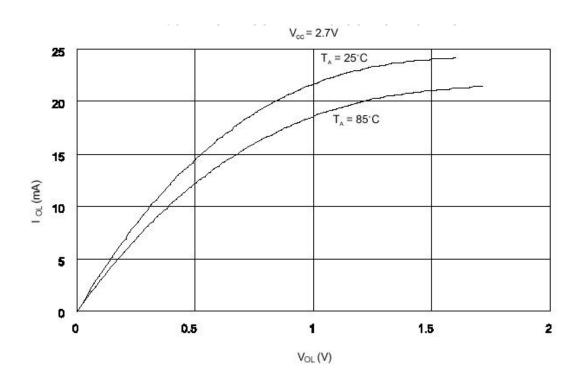

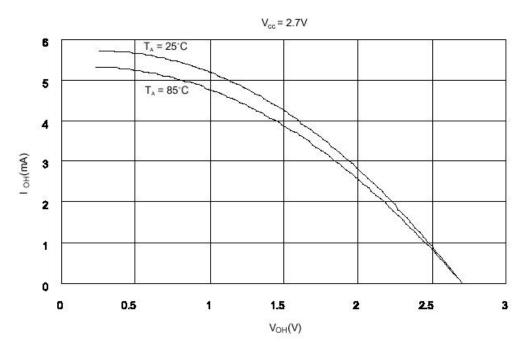

図 53 I/O ピンシンク電流対出力電圧

図 54 I/O ピンソース電流対出力電圧

図 55 I/O ピンシンク電流対出力電圧

図 56 I/O ピンソース電流対出力電圧

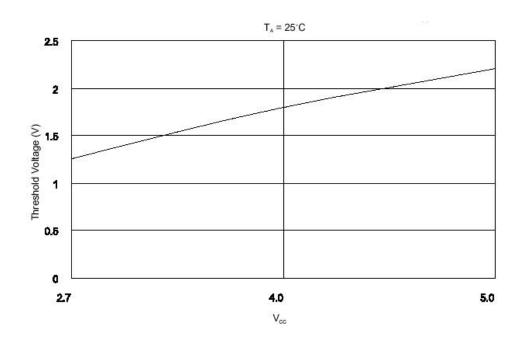

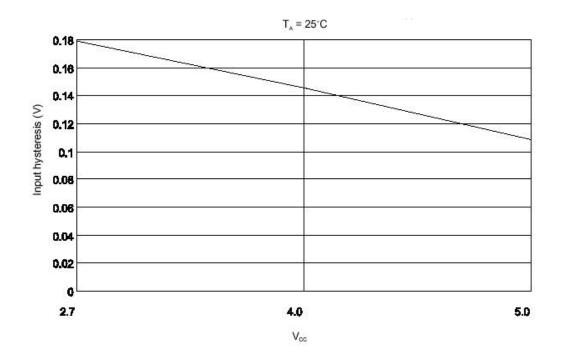

入力スレッシュホールドはヒステリシスの中心で測定しています。

図 57 I/O ピン入力スレッシューホールド電圧対 Vcc

### 図 58 I/O ピン入力ヒステリシス対 Vcc

#### AT90S1200 レジスタ概要

|                                              |                                                          | T          |       |               |               |                |               |               |             |

|----------------------------------------------|----------------------------------------------------------|------------|-------|---------------|---------------|----------------|---------------|---------------|-------------|

| Address                                      | Name                                                     | Bit 7      | Bit 6 | Bit 5         | Bit 4         | Bit 3          | Bit 2         | Bit 1         | Bit 0       |

| \$3F                                         | SREG                                                     | 3.         | T)    | Н             | S             | V              | N             | Z             | С           |

| \$3E                                         | Reserved                                                 | S 88       |       |               | 20 70         | W 10           |               | *             | 2           |

| \$3D                                         | Reserved                                                 | T          |       |               |               |                |               |               |             |

| \$3C                                         | Reserved                                                 |            |       |               | V4: V4:       | ev es          |               |               | a.          |

| \$3B                                         | GIMSK                                                    | -          | INT0  | 4.            |               | +              | +             | +             |             |

| \$3A                                         | Reserved                                                 | 0          |       |               |               |                |               |               |             |

| \$39                                         | TIMSK                                                    |            | ,     |               | i :- ii       |                | *             | TOIE0         |             |

| \$38                                         | TIFR                                                     |            | -     | 4             | - 3           | 2 - 1          | +             | TOV0          |             |

| \$37                                         | Reserved                                                 | 8          |       |               |               |                |               | e consum e    |             |

| \$36                                         | Reserved                                                 |            |       |               |               |                |               |               |             |

| \$35                                         | MCUCR                                                    |            | ,     | SE            | SM            |                |               | ISC01         | ISCO        |

| \$34                                         | Reserved                                                 |            |       |               |               |                |               |               |             |

| \$33                                         | TCCR0                                                    |            |       | 11.71         | ) er ()       |                | CS02          | CS01          | CS0         |